# **TLE 6244X**

# **18 Channel Smart Lowside Switch**

**ASSP for Powertrain**

**Data Sheet**

# **Features**

- Short Circuit Protection

- Overtemperature Protection

- Overvoltage Protection

- 16 bit Serial Data Input and Diagnostic Output (2 bit/chan. acc. SPI Protocol)

- Direct Parallel Control of 16 channels for PWM Applications

- Low Quiescent Current

- Compatible with 3.3V Microcontrollers

- Electrostatic discharge (ESD) Protection

- Green Product (RoHS-compliant)

- AEC gualified

RoHS

# **General description**

18-fold Low-Side Switch (0.35  $\Omega$  to 1  $\Omega$ ) in Smart Power Technology (SPT) with a Serial Peripheral Interface (SPI) and 18 open drain DMOS output stages. The TLE6244X is protected by embedded protection functions and designed for automotive and industrial applications. The output stages are controlled via SPI Interface. Additionally 16 of the 18 channels can be controlled direct in parallel for PWM applications. Therefore the TLE6244X is particularly suitable for engine management and powertrain systems.

# 1. Description

### 1.1 Short Description

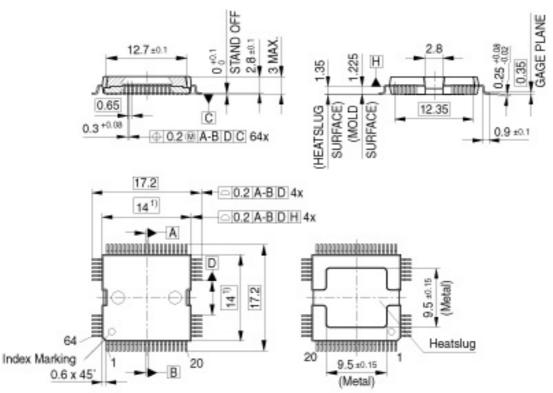

This circuit is available in PG-MQFP-64 package or as chip.

#### 1.1.1 Features of the Power Stages

|                 | Nominal Current | R <sub>on,max</sub> at T <sub>J</sub> = 25°C | static current limita-<br>tion enabled by SPI | Clamping |

|-----------------|-----------------|----------------------------------------------|-----------------------------------------------|----------|

| OUT1, 2, 5, 6   | 2.2A            | 400mΩ                                        | -                                             | 70V      |

| OUT3, OUT4      | 2.2A            | 380mΩ                                        | -                                             | 70V      |

| OUT7, OUT8      | 1.1A            | 780mΩ                                        | -                                             | 45V      |

| OUT9, OUT10     | 2.2A            | 380mΩ                                        | Х                                             | 45V      |

| OUT11OUT14      | 2.2A            | 380mΩ                                        | -                                             | 45V      |

| OUT15, OUT16    | 3.0A            | 280mΩ                                        | Х                                             | 45V      |

| OUT17, OUT18 *) | 1.1A            | 780mΩ                                        | Х                                             | 45V      |

\*) only serial control possible (via SPI)

Parallel connection of power stages is possible (see 1.13) Internal short-circuit protection Phase relation: non-inverting (exception: IN8->OUT8 is inverting)

### 1.1.2 Diagnostic Features

The following types of error can be detected: Short-circuit to U<sub>Batt</sub> (SCB) Short-circuit to ground (SCG) Open load (OL) Overtemperature (OT) Individual detection for each output. Serial transmission of the error code via SPI.

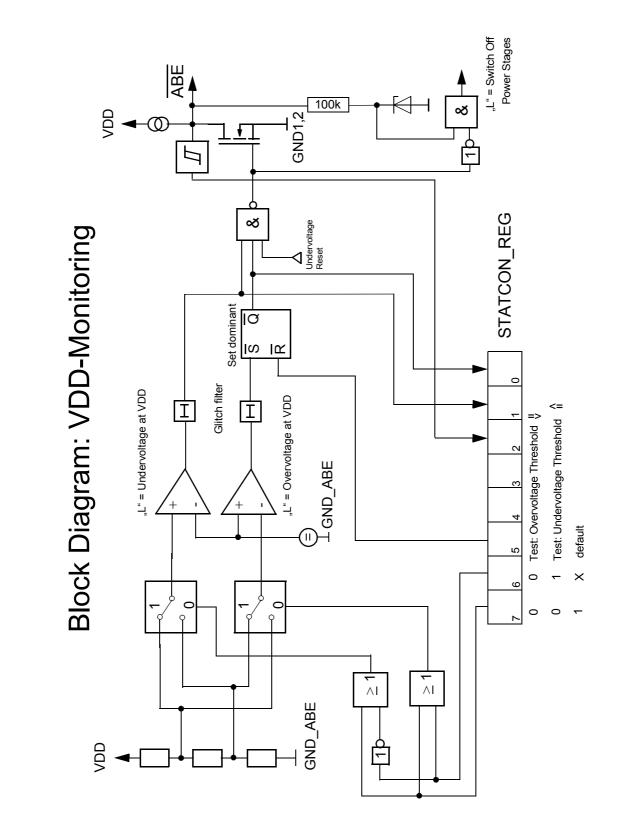

### 1.1.3 VDD-Monitoring

Low signal at pin ABE and shut-off of the power stages if VDD is out of the permitted range. Exception: If OUT8 is controlled by IN8, OUT8 will only be switched off by the overvoltage detection and not by undervoltage detection. The state of VDD can be read out via SPI.

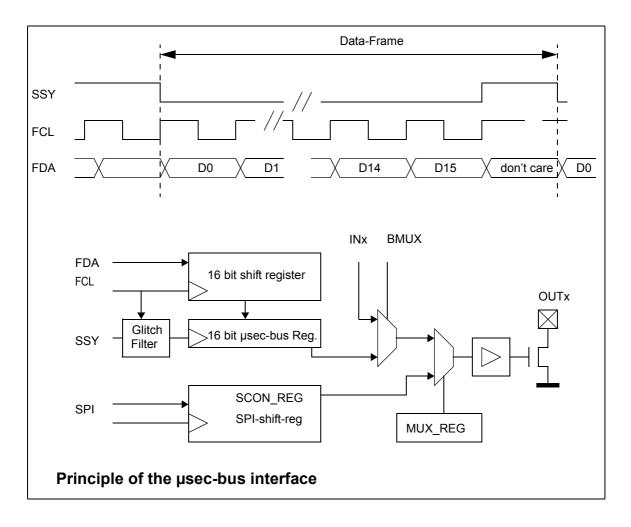

### 1.1.4 µsec-bus

Alternatively to the parallel and SPI control of the power stages, a high speed serial bus interface can be configured as control of the power stages OUT1...OUT7 and OUT9...OUT16.

#### 1.1.5 Power Stage OUT8

OUT8 can be controlled by SPI or by the pin IN8 only. When controlled by IN8 this power stage is functional if the voltage at the pin VDD is above 3,5V. OUT8 will not be reset by RST. In SPI mode the power stage is fully supervised by the VDD-monitor.

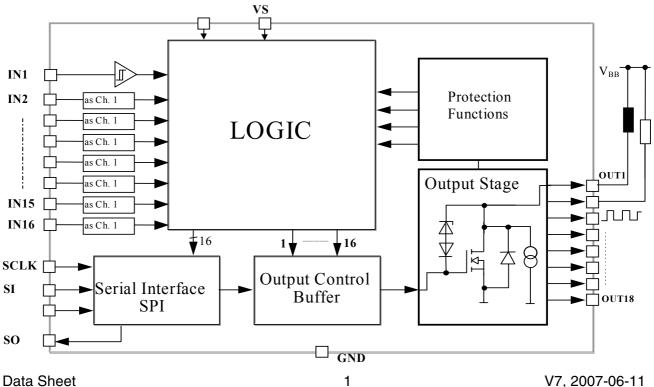

# 1.2 Block Diagram

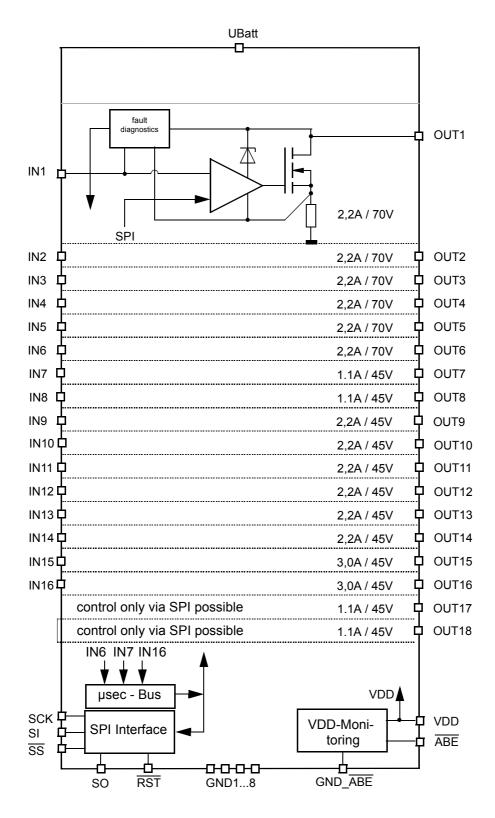

#### 1.3 Description of the Power Stages

### OUT1... OUT6

6 non-inverting low side power switches for nominal currents up to 2.2A. Control is possible by input pins, by the µsec-bus or via SPI. For  $T_J = 25^{\circ}$ C the on-resistance of the power switches is below 400m $\Omega$ .

An integrated zener diode limits the output voltage to 70V typically.

A protection for inverse current is implemented for OUT1... OUT4 for use as stepper-motor control.

#### OUT9... OUT14

6 non-inverting low side power switches for nominal currents up to 2.2A. Control is possible by input pins, by the µsec-bus or via SPI. For  $T_J = 25^{\circ}$ C the on-resistance of the power switches is below 380m $\Omega$ .

An integrated zener diode limits the output voltage to 45V typically.

#### **OUT15, OUT16**

2 non-inverting low side power switches for nominal currents up to 3.0A. Control is possible by input pins, by the µsec-bus or via SPI. For  $T_J = 25^{\circ}$ C the on-resistance of the power switches is below 280m $\Omega$ .

An integrated zener diode limits the output voltage to 45V typically.

## **OUT7, OUT8, OUT17, OUT18**

4 low side power switches for nominal currents up to 1100mA. Stage 7 is non-inverting, Stage 8 is inverting (IN8 = '1' => OUT8 is active). For the output OUT7 control is possible by the input pin, by the µsec-bus or via SPI, OUT8 is controlled by the input pin IN8 or via SPI, for the outputs OUT17 and OUT18 control is only possible via SPI. For  $T_J = 25^{\circ}$ C the on-resistance of the power switches is below 780m $\Omega$ .

An integrated zener diode limits the output voltage to 45V typically.

In order to increase the switching current or to reduce the power dissipation parallel connection of power stages is possible (for additional information see 1.13).

The power stages are short-circuit proof:

Power stages **OUT1...OUT8**, **OUT11.14**: In case of overload (SCB) they will be turned off after a given delay time. During this delay time the output current is limited by an internal current control loop.

Power stages OUT9, OUT10, OUT15...OUT18:

In case of SCB these power stages can be configured for a shut-down mode or for static current limitation. In the shut down mode while SCB they will behave like OUT1..8 or OUT11..14.

In case of static current limitation and SCB the current is limited and the corresponding bit combination is set (early warning) after a given delay time. They will not be turned off. If this condition leads to an overtemperature condition, the output will be set into a low duty cycle PWM (selective thermal shut- down with restart) to prevent critical chip temperature.

There are 3 possibilities to turn the power stages on again:

- turn the power stage off and on, either via serial control (SPI) or via parallel control (input pin, except outputs OUT17 and OUT18) or by the µsec-bus (except OUT8, OUT17,OUT18)

- applying a reset signal.

- sending the instruction "del\_dia" by the SPI-interface

The VDD-monitoring locks all power stages, except OUT8 for access by the IN8 input. OUT8 is locked by an internal threshold of 3,5V maximum when controlled by IN8. Otherwise OUT8 is locked by the VDD-monitor.

All low side switches are equipped with fault diagnostic functions:

- short-circuit to U<sub>Batt</sub>: (SCB) can be detected if switches are turned on

- short-circuit to ground: (SCG) can be detected if switches are turned off

- open load: (OL) can be detected if switches are turned off

- overtemperature: (OT) will only be detected if switches are turned on

The fault conditions SCB, SCG, OL and OT will not be stored until an integrated filtering time is expired (please note for PWM application). If, at one output, several errors occur in a sequence, always the last detected error will be stored (with filtering time). All fault conditions are encoded in two bits per switch and are stored in the corresponding SPI registers. Additionally there are two central diagnostic bits: one specially for OT and one for fault occurrence at any output.

The registers can be read out via SPI. After each read out cycle the registers have to be cleared by the DEL\_DIA command.

#### 1.3.1 Power Stage OUT8 (Condensed Description)

1.3.1.1 Control of OUT8 and VDD-Monitoring

OUT8 can be controlled by SPI or by the pin IN8 only, control by µs-bus is not possible. When controlled by IN8 this power stage is functional if the voltage at the pin VDD is above 3,5V. In SPI mode the power stage is fully supervised by the VDD-monitor. If OUT8 is controlled by IN8, OUT8 will only be switched off by the overvoltage detection and

If OUT8 is controlled by IN8, OUT8 will only be switched off by the overvoltage detection and not by undervoltage detection.

1.3.1.2 Phase Relation IN8 - OUT8

The phase relation IN8 -> OUT8 is inverting.

OUT8 is active if IN8 is set to logic '1' (high level, see 3.4.2 ) in case of parallel access.

On executing the read instruction on RD\_INP1/2 the inverted status of IN8 is read back.

#### 1.3.1.3 Reset / Power Stage Diagnostics

If OUT8 is controlled by IN8, OUT8 will not be reseted by RST.

After reset parallel control (by IN8) is active for OUT8.

If UVDD < 4.5V errors are not stored because of the active RST of the external Regulator. Nevertheless

OUT8 is protected against overload.

1.3.1.4 Input Current

The control input IN8 has an internal pull-down current source. Thus the input currents I IN8 are positive (flow into the pin).

1.3.1.5 On Resistance

For OUT8 and 3.5V < UVDD < 4.5V R on increases (see 3.8.5).

1.3.1.6 Parallel Connection of Power Stages

Parallel connection of power stages with OUT8 and parallel control is prohibited (inverting input IN8). Control via SPI is possible. See 1.13.

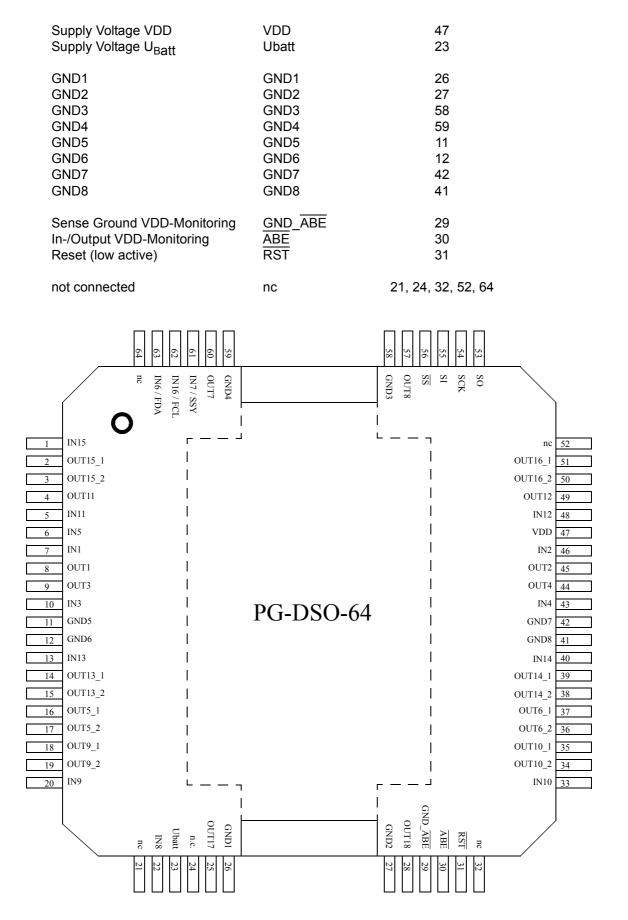

# 1.4 Pinout

| Function<br>Input 1<br>Input 2<br>Input 3<br>Input 4<br>Input 5<br>Input 6 or FDA<br>Input 7 or SSY<br>Input 8<br>Input 9<br>Input 10<br>Input 11<br>Input 12<br>Input 13<br>Input 14<br>Input 15<br>Input 16 or FCL                                                                                                                                                                                                                                                   | Pin<br>IN1<br>IN2<br>IN3<br>IN4<br>IN5<br>IN6<br>IN7<br>IN8<br>IN7<br>IN8<br>IN9<br>IN10<br>IN11<br>IN12<br>IN13<br>IN14<br>IN15<br>IN16                                                                                                                                                                                                                                                             | Pin Number<br>7<br>46<br>10<br>43<br>6<br>63<br>61<br>22<br>20<br>33<br>5<br>48<br>13<br>40<br>1<br>62                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output 1<br>Output 2<br>Output 3<br>Output 4<br>Output 5_1<br>Output 5_2<br>Output 6_1<br>Output 6_2<br>Output 6_2<br>Output 7<br>Output 8<br>Output 9_1<br>Output 9_1<br>Output 9_2<br>Output 10_1<br>Output 10_2<br>Output 10_2<br>Output 11<br>Output 12<br>Output 13_1<br>Output 13_2<br>Output 13_1<br>Output 13_2<br>Output 14_1<br>Output 14_2<br>Output 15_1<br>Output 15_2<br>Output 16_1<br>Output 16_2<br>Output 17<br>Output 18<br>(Note: OUTxy_1 and OUT) | OUT1<br>OUT2<br>OUT3<br>OUT4<br>OUT5_1<br>OUT5_2<br>OUT6_1<br>OUT6_2<br>OUT6_2<br>OUT7<br>OUT8<br>OUT9_1<br>OUT9_1<br>OUT9_2<br>OUT10_1<br>OUT9_2<br>OUT10_1<br>OUT10_2<br>OUT11_1<br>OUT12<br>OUT13_1<br>OUT13_2<br>OUT14_1<br>OUT13_2<br>OUT14_1<br>OUT14_2<br>OUT15_1<br>OUT15_2<br>OUT15_1<br>OUT15_2<br>OUT16_1<br>OUT16_2<br>OUT16_1<br>OUT16_2<br>OUT17<br>OUT18<br>xy_2 have to be connected | 8<br>45<br>9<br>44<br>16<br>17<br>37<br>36<br>60<br>57<br>18<br>19<br>35<br>34<br>4<br>4<br>9<br>14<br>15<br>39<br>38<br>2<br>3<br>38<br>2<br>3<br>38<br>2<br>3<br>51<br>50<br>25<br>28<br>ed externally!) |

| Slave Select<br>Serial Output<br>Serial Input<br>SPI Clock                                                                                                                                                                                                                                                                                                                                                                                                             | SS<br>SO<br>SI<br>SCK                                                                                                                                                                                                                                                                                                                                                                                | 56<br>53<br>55<br>54                                                                                                                                                                                       |

## 1.5 Function of Pins

| IN1 to IN16                | Control inputs of the power stages                                                                                                                                |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Internal pull-up current sources (exception: IN8 with pull-down current source)                                                                                   |

| FCL<br>FDA<br>SSY          | Clock for the µsec-bus (pin shared with IN16)<br>Data for the µsec-bus (pin shared with IN6)<br>Strobe and Synchronisation for the µsec-bus (pin shared with IN7) |

| OUT1 to OUT18              | Outputs of the power switches                                                                                                                                     |

|                            | Short-circuit proof<br>Low side switches<br>Limitation of the output voltage by zener diodes                                                                      |

| VDD                        | Supply voltage 5V                                                                                                                                                 |

| UBatt                      | Supply voltage U <sub>Batt</sub>                                                                                                                                  |

|                            | Pin must not be left open but has to be connected either to $\rm U_{Batt}$ or to $\rm V_{DD}$ (e.g. in commercial vehicles)                                       |

| GND1 to GND8               | Ground pins                                                                                                                                                       |

|                            | Ground pins for the power stages (see 2.4)<br>Ground reference of all logic signals is GND1/2                                                                     |

| RST                        | Reset                                                                                                                                                             |

|                            | Active low<br>Locks all power switches regardless of their input signals (except OUT8)<br>Clears the fault registers<br>Resets the µsec-bus interface registers   |

| ABE                        | In-/Output VDD-Monitoring                                                                                                                                         |

|                            | Active low<br>Output pin for the VDD-Monitoring<br>Input pin for the shut-off signal coming from the supervisor                                                   |

| GND_ABE                    | Sense ground VDD-Monitoring                                                                                                                                       |

| SI, SO, SCK, <del>SS</del> | SPI Interface                                                                                                                                                     |

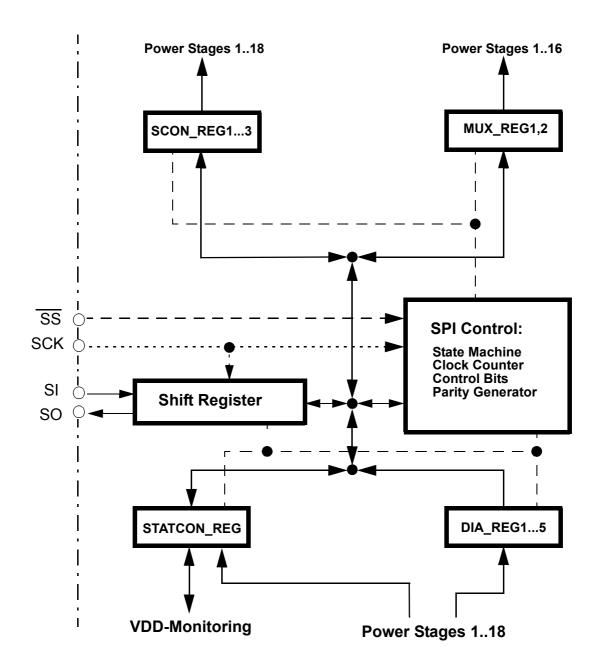

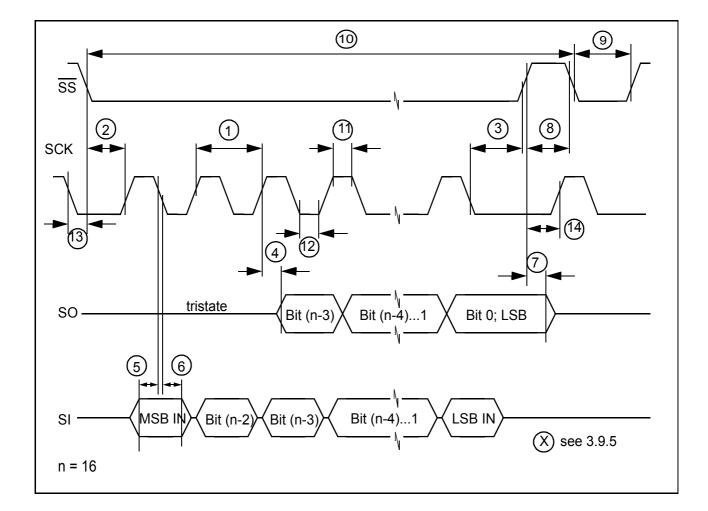

#### 1.6 SPI Interface

The serial SPI interface establishes a communication link between TLE6244X and the systems microcontroller. TLE6244X always operates in slave mode whereas the controller provides the master function. The maximum baud rate is 5 MBaud.

The TLE6244X is selected by the SPI master by an active slave select signal at  $\overline{SS}$  and by the first two bits of the SPI instruction.SI is the data input (Slave In), SO the data output (Slave Out). Via SCK (Serial Clock Input) the SPI clock is provided by the master.

In case of inactive slave select signal (High) the data output SO goes into tristate.

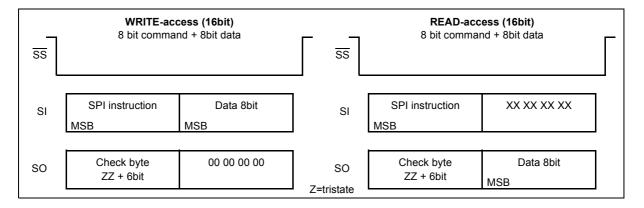

#### **Block Diagram:**

A SPI communication always starts with a SPI instruction sent from the controller to TLE6244X. During a write cycle the controller sends the data after the SPI instruction, beginning with the MSB. During a reading cycle, after having received the SPI instruction, TLE6244X sends the corresponding data to the controller, also starting with the MSB.

#### SPI Command/Format:

| MSB |   |        |        |        |        |        |      |

|-----|---|--------|--------|--------|--------|--------|------|

| 7   | 6 | 5      | 4      | 3      | 2      | 1      | 0    |

| 0   | 0 | INSTR4 | INSTR3 | INSTR2 | INSTR1 | INSTR0 | INSW |

| Bit | Name        | Description                       |

|-----|-------------|-----------------------------------|

| 7,6 | CPAD1,0     | Chip Address (has to be '0', '0') |

| 5-1 | INSTR (4-0) | SPI instruction (encoding)        |

| 0   | INSW        | Parity of the instruction         |

#### Characteristics of the SPI Interface:

- 1) If the slave select signal at  $\overline{SS}$  is High, the SPI-logic is set on default condition, i.e. it expects an instruction.

- If the 5V-reset (RST) is active, the SPI output SO is switched into tristate. The VDD monitoring (ABE) has no influence on the SPI interface.

- 3) Verification byte:

Simultaneously to the receipt of an SPI instruction TLE6244X transmits a verification byte via the output SO to the controller. This byte indicates regular or irregular operation of the SPI. It contains an initial bit pattern and a flag indicating an invalid instruction of the previous access.

4) On a read access the databits at the SPI input SI are rejected. On a writing access or after the DEL\_DIA instruction the TLE6244XTLE6244X sets the SPI output SO to low after sending the verification byte. If more than 16 bits are received the rest of the frame is rejected.

- 5) Invalid instruction/access:

- An instruction is invalid, if one of the following conditions is fulfilled:

- an unused instruction code is detected (see tables with SPI instructions)

- in case the previous transmission is not completed in terms of internal data processing

- number of SPI clock pulses counted during active SS differs from exactly 16 clock pulses. A write access and the instruction DEL\_DIA is internally suppressed (i.e internal registers will not be affected) in all cases where at the rising (inactive) edge of SS the number of falling edges applied to the SPI input SCK during the access is not equal to 16. A write access is also internally suppressed (i.e internal registers will not be affected) if at the rising (inactive) edge of SS a 17th bit is submitted (SCK='1').

After the bits CPAD1,0 and INSTR (4-0) have been sent from the microcontroller TLE6244X is able to check if the instruction code is valid. If an invalid instruction is detected, any modification on a register of TLE6244X is not allowed and the data byte 'FFh' is transmitted after having sent the verification byte. If a valid read instruction is detected the content of the corresponding register is transmitted to the controller after having sent the verification byte (even if bit INSW afterwards is wrong). If a valid write instruction is

detected the data byte '00h' is transmitted to the controller after having sent the verification byte (even if bit INSW afterwards is wrong) but modifications on any register of TLE6244 are not allowed until bit INSW is valid, too.

If an invalid instruction is detected bit TRANS\_F in the following verification byte is set to 'High'. This bit must not be cleared before it has been sent to the microcontroller.

6) If TLE6244X and additional IC's are connected to one common slave select, they are distinguished by the chip address (CPAD1, CPAD0). If an IC with 32bit-transmission-format is selected, TLE6232 must not be activated, even if slave select is set to 'low' and the first two bits of the third byte of the 32bit-transmission are identical to the chip address of TLE6244X.

During the transmission of CPAD1 and CPAD0 the data output SO remains in tristate (see timing diagram of the SPI in chapter 3.9.).

#### SPI access format:

#### Verification byte:

| MSB |   |   |   |   |   |   |         |

|-----|---|---|---|---|---|---|---------|

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

| Z   | Z | 1 | 0 | 1 | 0 | 1 | TRANS_F |

| Bit | Name    | Description                                                                                                                    |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------|

| 0   | TRANS_F | Bit = 1: error detected during previous transfer<br>Bit = 0: previous transfer was recognised as valid<br>State after reset: 0 |

| 1   |         | Fixed to High                                                                                                                  |

| 2   |         | Fixed to Low                                                                                                                   |

| 3   |         | Fixed to High                                                                                                                  |

| 4   |         | Fixed to Low                                                                                                                   |

| 5   |         | Fixed to High                                                                                                                  |

| 6   |         | send as high impedance                                                                                                         |

| 7   |         | send as high impedance                                                                                                         |

# **SPI Instructions**

Intineon technologies

| SPI Instruction | Encodi             | ng                         |        | Description                                  |  |  |

|-----------------|--------------------|----------------------------|--------|----------------------------------------------|--|--|

|                 | bit 7,6<br>CPAD1,0 | bit 5,4,3,2,1<br>INSTR(40) | Parity |                                              |  |  |

| RD_IDENT1       | 00                 | 00000                      | 0      | read identifier 1                            |  |  |

| RD_IDENT2       | 00                 | 00001                      | 1      | read identifier2                             |  |  |

|                 | ·                  | ·                          |        |                                              |  |  |

| WR_STATCON      | 00                 | 10001                      | 0      | write into STATCON_REG                       |  |  |

| WR_MUX1         | 00                 | 10010                      | 0      | write into MUX_REG1                          |  |  |

| WR_MUX2         | 00                 | 10011                      | 1      | write into MUX_REG2                          |  |  |

| WR_SCON1        | 00                 | 10100                      | 0      | write into SCON_REG1                         |  |  |

| WR_SCON2        | 00                 | 10101                      | 1      | write into SCON_REG2                         |  |  |

| WR_SCON3        | 00                 | 10110                      | 1      | write into SCON_REG3                         |  |  |

| WR_CONFIG       | 00                 | 10111                      | 0      | write into CONFIG                            |  |  |

|                 |                    |                            |        |                                              |  |  |

| RD_MUX1         | 00                 | 00010                      | 1      | read MUX_REG1                                |  |  |

| RD_MUX2         | 00                 | 00011                      | 0      | read MUX_REG2                                |  |  |

| RD_SCON1        | 00                 | 00100                      | 1      | read SCON_REG1                               |  |  |

| RD_SCON2        | 00                 | 00101                      | 0      | read SCON_REG2                               |  |  |

| RD_SCON3        | 00                 | 00110                      | 0      | read SCON_REG3                               |  |  |

| RD_STATCON      | 00                 | 00111                      | 1      | read STATCON_REG                             |  |  |

| DEL_DIA         | 00                 | 11000                      | 0      | resets the 5 diagnostic registers<br>DIA_REG |  |  |

| RD_DIA1         | 00                 | 01000                      | 1      | read DIA_REG1                                |  |  |

| RD_DIA2         | 00                 | 01001                      | 0      | read DIA_REG2                                |  |  |

| RD_DIA3         | 00                 | 01010                      | 0      | read DIA_REG3                                |  |  |

| RD_DIA4         | 00                 | 01011                      | 1      | read DIA_REG4                                |  |  |

| RD_DIA5         | 00                 | 01100                      | 0      | read DIA_REG5                                |  |  |

| RD_CONFIG       | 00                 | 01101                      | 1      | read CONFIG                                  |  |  |

| RD_INP1         | 00                 | 01110                      | 1      | read INP_REG1                                |  |  |

| RD_INP2         | 00                 | 01111                      | 0      | read INP_REG2                                |  |  |

|                 |                    | all others                 |        | no function                                  |  |  |

#### 1.6.1 Serial/Parallel Control

Serial/Parallel Control of the Power Stages 1...16 and Serial Control (SPI) of the Power Stages 17 and 18:

The registers MUX\_REG1/2 and the bmux-bit prescribe parallel control or serial control (SPI or µsecbus) of the power stages.

#### (SPI-Instructions: WR\_MUX1...2, RD\_MUX1...2, WR\_SCON1...3, RD\_SCON1...3)

The following table shows the truth table for the control of the power stages 1...18. The registers MUX\_REG1, 2 prescribe parallel-control or serial control of the power stages. The registers SCON\_REG1...3 prescribe the state of the power stage in case of SPI-serial control. BMUX determines parallel control or control by µsec-bus.

For the power stages 17 and 18 control is exclusively possible via SCON17/18. IN17/18 and MUX17/18 do **not** exist. BMUX has no function for OUT17/18.

| ABE | RST | INx | BMUX | MUXx | SCONx | µsec-<br>REGx | Output OUTx of Power Stage x,<br>x = 118 |

|-----|-----|-----|------|------|-------|---------------|------------------------------------------|

| 0   | 0   | Х   | Х    | Х    | Х     | Х             | OUTx off                                 |

| 0   | 1   | Х   | Х    | Х    | Х     | Х             | OUTx off                                 |

| 1   | 0   | Х   | Х    | Х    | Х     | Х             | OUTx off                                 |

| 1   | 1   | Х   | Х    | 0    | 0     | Х             | SPI Control: OUTx on                     |

| 1   | 1   | Х   | Х    | 0    | 1     | Х             | SPI Control: OUTx off                    |

| 1   | 1   | 0   | 1    | 1    | Х     | Х             | Parallel Control: OUTx on                |

| 1   | 1   | 1   | 1    | 1    | Х     | Х             | Parallel Control: OUTx off               |

| 1   | 1   | Х   | 0    | 1    | Х     | 0             | µsec-bus Control: OUTx on                |

| 1   | 1   | Х   | 0    | 1    | Х     | 1             | µsec-bus Control: OUTx off               |

Exception: OUT8 is on (active) if IN8 is set to logic '1' (and off if IN8 is set to logic '0') in case of parallel access.

Note: OUT8 cannot be controlled by the µsec-Bus. Refer to section 1.7.

# Description of the SPI Registers

| Register: MUX_REG1 |      |      |      |      |      |      |      |  |

|--------------------|------|------|------|------|------|------|------|--|

| 7                  | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

| MUX7               | MUX6 | MUX5 | MUX4 | MUX3 | MUX2 | MUX1 | MUX0 |  |

| State of | State of Reset: 80H              |                                             |  |  |  |  |  |

|----------|----------------------------------|---------------------------------------------|--|--|--|--|--|

| Access   | Access by Controller: Read/Write |                                             |  |  |  |  |  |

| Bit      | Name                             | Description                                 |  |  |  |  |  |

| 0        | MUX0                             | Serial or parallel control of power stage 1 |  |  |  |  |  |

| 1        | MUX1                             | Serial or parallel control of power stage 2 |  |  |  |  |  |

| 2        | MUX2                             | Serial or parallel control of power stage 3 |  |  |  |  |  |

| 3        | MUX3                             | Serial or parallel control of power stage 4 |  |  |  |  |  |

| 4        | MUX4                             | Serial or parallel control of power stage 5 |  |  |  |  |  |

| 5        | MUX5                             | Serial or parallel control of power stage 6 |  |  |  |  |  |

| 6        | MUX6                             | Serial or parallel control of power stage 7 |  |  |  |  |  |

| 7        | MUX7                             | Serial or parallel control of power stage 8 |  |  |  |  |  |

| Register: MUX_REG2 |       |       |       |       |       |      |      |  |

|--------------------|-------|-------|-------|-------|-------|------|------|--|

| 7                  | 6     | 5     | 4     | 3     | 2     | 1    | 0    |  |

| MUX15              | MUX14 | MUX13 | MUX12 | MUX11 | MUX10 | MUX9 | MUX8 |  |

| State of | State of Reset: 00H              |                                              |  |  |  |  |

|----------|----------------------------------|----------------------------------------------|--|--|--|--|

| Access   | Access by Controller: Read/Write |                                              |  |  |  |  |

| Bit      | Name                             | Description                                  |  |  |  |  |

| 0        | MUX8                             | Serial or parallel control of power stage 9  |  |  |  |  |

| 1        | MUX9                             | Serial or parallel control of power stage 10 |  |  |  |  |

| 2        | MUX10                            | Serial or parallel control of power stage 11 |  |  |  |  |

| 3        | MUX11                            | Serial or parallel control of power stage 12 |  |  |  |  |

| 4        | MUX12                            | Serial or parallel control of power stage 13 |  |  |  |  |

| 5        | MUX13                            | Serial or parallel control of power stage 14 |  |  |  |  |

| 6        | MUX14                            | Serial or parallel control of power stage 15 |  |  |  |  |

| 7        | MUX15                            | Serial or parallel control of power stage 16 |  |  |  |  |

| Register | ": SCON_F                                              | REG1       |                                          |                                          |              |       |       |  |  |

|----------|--------------------------------------------------------|------------|------------------------------------------|------------------------------------------|--------------|-------|-------|--|--|

| 7        | 6                                                      | 5          | 4                                        | 3                                        | 2            | 1     | 0     |  |  |

| SCON7    | SCON6                                                  | SCON5      | SCON4                                    | SCON3                                    | SCON2        | SCON1 | SCON0 |  |  |

|          | State of Reset: FFH                                    |            |                                          |                                          |              |       |       |  |  |

| Access   | by Controlle                                           | er: Read/V | Vrite                                    |                                          |              |       |       |  |  |

| Bit      | Name                                                   |            | Descriptio                               | Description                              |              |       |       |  |  |

| 0        | SCON0                                                  |            | State of se                              | State of serial control of power stage 1 |              |       |       |  |  |

| 1        | SCON1                                                  |            | State of se                              | State of serial control of power stage 2 |              |       |       |  |  |

| 2        | SCON2                                                  |            | State of se                              | State of serial control of power stage 3 |              |       |       |  |  |

| 3        | SCON3                                                  |            | State of se                              | erial control o                          | f power stag | e 4   |       |  |  |

| 4        | SCON4                                                  |            | State of serial control of power stage 5 |                                          |              |       |       |  |  |

| 5        | SCON5                                                  |            | State of serial control of power stage 6 |                                          |              |       |       |  |  |

| 6        | SCON6                                                  |            | State of se                              | State of serial control of power stage 7 |              |       |       |  |  |

| 7        | SCON7         State of serial control of power stage 8 |            |                                          |                                          |              | e 8   |       |  |  |

| Register: SCON_REG2 |        |        |        |        |        |       |       |

|---------------------|--------|--------|--------|--------|--------|-------|-------|

| 7                   | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

| SCON15              | SCON14 | SCON13 | SCON12 | SCON11 | SCON10 | SCON9 | SCON8 |

|     | State of Reset: FFH Access by Controller: Read/Write |                                           |  |  |  |  |

|-----|------------------------------------------------------|-------------------------------------------|--|--|--|--|

| Bit | Name                                                 | Description                               |  |  |  |  |

| 0   | SCON8                                                | State of serial control of power stage 9  |  |  |  |  |

| 1   | SCON9                                                | State of serial control of power stage 10 |  |  |  |  |

| 2   | SCON10                                               | State of serial control of power stage 11 |  |  |  |  |

| 3   | SCON11                                               | State of serial control of power stage 12 |  |  |  |  |

| 4   | SCON12                                               | State of serial control of power stage 13 |  |  |  |  |

| 5   | SCON13                                               | State of serial control of power stage 14 |  |  |  |  |

| 6   | SCON14                                               | State of serial control of power stage 15 |  |  |  |  |

| 7   | SCON15                                               | State of serial control of power stage 16 |  |  |  |  |

| Register | : SCON_F | SCON_REG3 |   |   |   |        |        |

|----------|----------|-----------|---|---|---|--------|--------|

| 7        | 6        | 5         | 4 | 3 | 2 | 1      | 0      |

| 1        | 1        | 1         | 1 | 1 | 1 | SCON17 | SCON16 |

| State of | State of Reset: FFH              |                                           |  |  |  |  |

|----------|----------------------------------|-------------------------------------------|--|--|--|--|

| Access   | Access by Controller: Read/Write |                                           |  |  |  |  |

| Bit      | Name                             | Description                               |  |  |  |  |

| 0        | SCON16                           | State of serial control of power stage 17 |  |  |  |  |

| 1        | SCON17                           | State of serial control of power stage 18 |  |  |  |  |

| 7-2      |                                  | No function: HIGH on reading              |  |  |  |  |

# 1.6.2 Diagnostics/Encoding of Failures

# **Description of the SPI Registers**

# (SPI Instructions: RD\_DIA1...5)

| Register | : DIA_RE | G1   |      |      |      |      |      |

|----------|----------|------|------|------|------|------|------|

| 7        | 6        | 5    | 4    | 3    | 2    | 1    | 0    |

| DIA7     | DIA6     | DIA5 | DIA4 | DIA3 | DIA2 | DIA1 | DIA0 |

| State o | State of Reset: FFH             |                                  |  |  |  |  |

|---------|---------------------------------|----------------------------------|--|--|--|--|

| Access  | Access by Controller: Read only |                                  |  |  |  |  |

| Bit     | Name                            | Description                      |  |  |  |  |

| 1-0     | DIA (1-0)                       | Diagnostic Bits of power stage 1 |  |  |  |  |

| 3-2     | DIA (3-2)                       | Diagnostic Bits of power stage 2 |  |  |  |  |

| 5-4     | DIA (5-4)                       | Diagnostic Bits of power stage 3 |  |  |  |  |

| 7-6     | DIA (7-6)                       | Diagnostic Bits of power stage 4 |  |  |  |  |

| Register | : DIA_RE | G2    |       |       |       |      |      |

|----------|----------|-------|-------|-------|-------|------|------|

| 7        | 6        | 5     | 4     | 3     | 2     | 1    | 0    |

| DIA15    | DIA14    | DIA13 | DIA12 | DIA11 | DIA10 | DIA9 | DIA8 |

| State o | State of Reset: FFH             |                                  |  |  |  |  |

|---------|---------------------------------|----------------------------------|--|--|--|--|

| Access  | Access by Controller: Read only |                                  |  |  |  |  |

| Bit     | Name                            | Description                      |  |  |  |  |

| 1-0     | DIA (9-8)                       | Diagnostic Bits of power stage 5 |  |  |  |  |

| 3-2     | DIA (11-10)                     | Diagnostic Bits of power stage 6 |  |  |  |  |

| 5-4     | DIA (13-12)                     | Diagnostic Bits of power stage 7 |  |  |  |  |

| 7-6     | DIA (15-14)                     | Diagnostic Bits of power stage 8 |  |  |  |  |

| Register | Register: DIA_REG3 |       |       |       |       |       |       |

|----------|--------------------|-------|-------|-------|-------|-------|-------|

| 7        | 6                  | 5     | 4     | 3     | 2     | 1     | 0     |

| DIA23    | DIA22              | DIA21 | DIA20 | DIA19 | DIA18 | DIA17 | DIA16 |

| State of             | State of Reset: FFH             |                                   |  |  |  |  |

|----------------------|---------------------------------|-----------------------------------|--|--|--|--|

| Access               | Access by Controller: Read only |                                   |  |  |  |  |

| Bit Name Description |                                 |                                   |  |  |  |  |

| 1-0                  | DIA (17-16)                     | Diagnostic Bits of power stage 9  |  |  |  |  |

| 3-2                  | DIA (19-18)                     | Diagnostic Bits of power stage 10 |  |  |  |  |

| 5-4                  | DIA (21-20)                     | Diagnostic Bits of power stage 11 |  |  |  |  |

| 7-6                  | DIA (23-22)                     | Diagnostic Bits of power stage 12 |  |  |  |  |

| Register | : DIA_RE | G4    |       |       |       |       |       |

|----------|----------|-------|-------|-------|-------|-------|-------|

| 7        | 6        | 5     | 4     | 3     | 2     | 1     | 0     |

| DIA31    | DIA30    | DIA29 | DIA28 | DIA27 | DIA26 | DIA25 | DIA24 |

| State of | Reset: FFH                      |                                   |  |  |  |  |

|----------|---------------------------------|-----------------------------------|--|--|--|--|

| Access   | Access by Controller: Read only |                                   |  |  |  |  |

| Bit      | Name                            | Description                       |  |  |  |  |

| 1-0      | DIA (25-24)                     | Diagnostic Bits of power stage 13 |  |  |  |  |

| 3-2      | DIA (27-26)                     | Diagnostic Bits of power stage 14 |  |  |  |  |

| 5-4      | DIA (29-28)                     | Diagnostic Bits of power stage 15 |  |  |  |  |

| 7-6      | DIA (31-30)                     | Diagnostic Bits of power stage 16 |  |  |  |  |

| Register | r: DIA_RE | G5 |       |       |       |       |       |

|----------|-----------|----|-------|-------|-------|-------|-------|

| 7        | 6         | 5  | 4     | 3     | 2     | 1     | 0     |

| 1        | 1         | 1  | UBatt | DIA35 | DIA34 | DIA33 | DIA32 |

| State of                        | Reset: FFH  |                                                                                                                                                                                                                     |  |  |  |

|---------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Access by Controller: Read only |             |                                                                                                                                                                                                                     |  |  |  |

| Bit Name Description            |             |                                                                                                                                                                                                                     |  |  |  |

| 1-0                             | DIA (33-32) | Diagnostic Bits of power stage 17                                                                                                                                                                                   |  |  |  |

| 3-2                             | DIA (35-34) | Diagnostic Bits of power stage 18                                                                                                                                                                                   |  |  |  |

| 4                               | UBatt       | 0: Voltage Level at Pin UBatt is below 2V (typically)<br>1: Voltage Level at Pin UBatt is above 2V (typically)<br>Diagnosis of UBatt is only possible if U <sub>VDD</sub> > 4.5V<br>Status of UBatt is not latched. |  |  |  |

| 7-5                             |             | No function: High on reading                                                                                                                                                                                        |  |  |  |

| Encoding of the | Encoding of the Diagnostic Bits of the Power Stages |                                               |  |  |  |  |  |

|-----------------|-----------------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| DIA(2*x-1)      | DIA(2*x-2)                                          | State of power stage x x = 118                |  |  |  |  |  |

| 1               | 1                                                   | Power stage o.k.                              |  |  |  |  |  |

| 1               | 0                                                   | Short-circuit to U <sub>Batt</sub> (SCB) / OT |  |  |  |  |  |

| 0               | 1                                                   | Open load (OL)                                |  |  |  |  |  |

| 0               | 0                                                   | Short-circuit to ground (SCG)                 |  |  |  |  |  |

### 1.6.3 Configuration

The  $\mu$ sec-bus is enabled by this register. In addition the shut off at SCB can be configured for the power-stages OUT9, OUT10 and OUT15... OUT18.

| CONFIG (Read and write) |         |         |        |         |         |      |   |

|-------------------------|---------|---------|--------|---------|---------|------|---|

| 7                       | 6       | 5       | 4      | 3       | 2       | 1    | 0 |

| O16-SCB                 | O15-SCB | O10-SCB | O9-SCB | O18-SCB | O17-SCB | BMUX | 1 |

| State o | of Reset: FFh |                                                                                                        |

|---------|---------------|--------------------------------------------------------------------------------------------------------|

| Bit     | Name          | Description                                                                                            |

| 0       |               | No function: HIGH on reading                                                                           |

| 1       | BMUX          | 1: parallel inputs INx enabled<br>0: µsec-Bus Interface enabled                                        |

| 2       | O17-SCB       | 1: The output OUT17 is switched off in case of SCB<br>0: The output is not switched off in case of SCB |

| 3       | O18-SCB       | 1: The output OUT18 is switched off in case of SCB<br>0: The output is not switched off in case of SCB |

| 4       | O9-SCB        | 1: The output OUT9 is switched off in case of SCB<br>0: The output is not switched off in case of SCB  |

| 5       | O10-SCB       | 1: The output OUT10 is switched off in case of SCB<br>0: The output is not switched off in case of SCB |

| 6       | O15-SCB       | 1: The output OUT15 is switched off in case of SCB<br>0: The output is not switched off in case of SCB |

| 7       | O16-SCB       | 1: The output OUT16 s switched off in case of SCB<br>0: The output is not switched off in case of SCB  |

Description of the µsec-bus see chapter 1.7

#### 1.6.4 Other

#### Reading the IC Identifier (SPI Instruction: RD\_IDENT1):

| IC Identifier1 (Device ID) |     |     |     |     |     |     |     |

|----------------------------|-----|-----|-----|-----|-----|-----|-----|

| 7                          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| ID7                        | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |

| Bit | Name   | Description      |

|-----|--------|------------------|

| 70  | ID(70) | ID-No.: 10101000 |

#### Reading the IC revision number (SPI Instruction: RD\_IDENT2):

| IC revis | ion number |      |      |      |      |      |      |

|----------|------------|------|------|------|------|------|------|

| 7        | 6          | 5    | 4    | 3    | 2    | 1    | 0    |

| SWR3     | SWR2       | SWR1 | SWR0 | MSR3 | MSR2 | MSR1 | MSR0 |

|          |            |      |      |      |      |      |      |

| Bit | Name    | Description                                      |

|-----|---------|--------------------------------------------------|

| 74  | SWR(30) | Revision corresponding to Software release: 0Hex |

| 30  | MSR(30) | Revision corresponding to Maskset: 0Hex          |

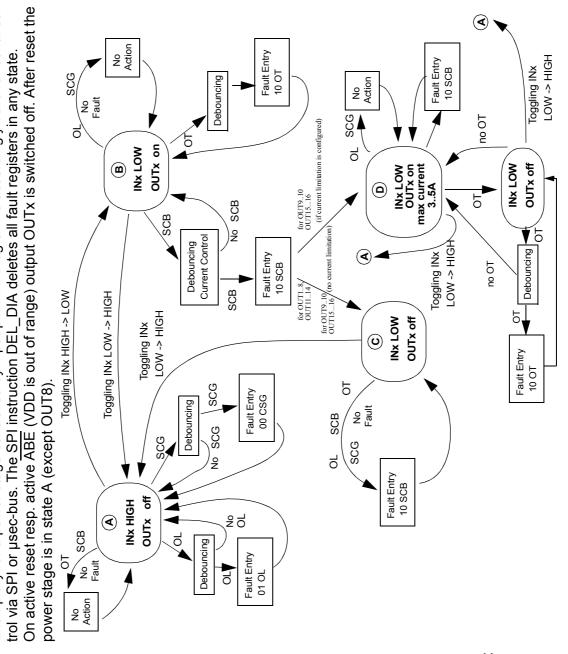

#### Reset of the Diagnostic Information (SPI Instruction: DEL\_DIA):

Resets the 5 diagnostic registers DIA\_REG1...5 to FFH and the common overtemperature flag in register STATCON\_REG (Bit4) to High. These bits are only cleared by the DEL\_DIA instruction when there is no failure entry at the input of the registers.

Access is performed like a writing access with any data byte.

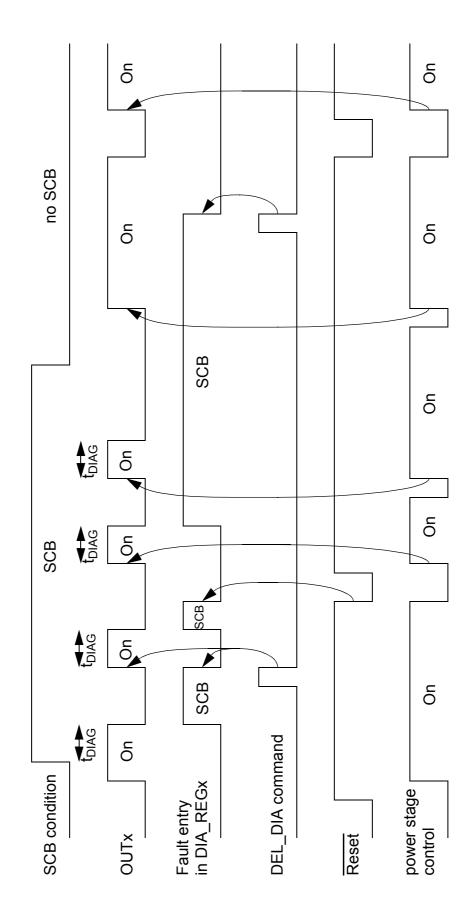

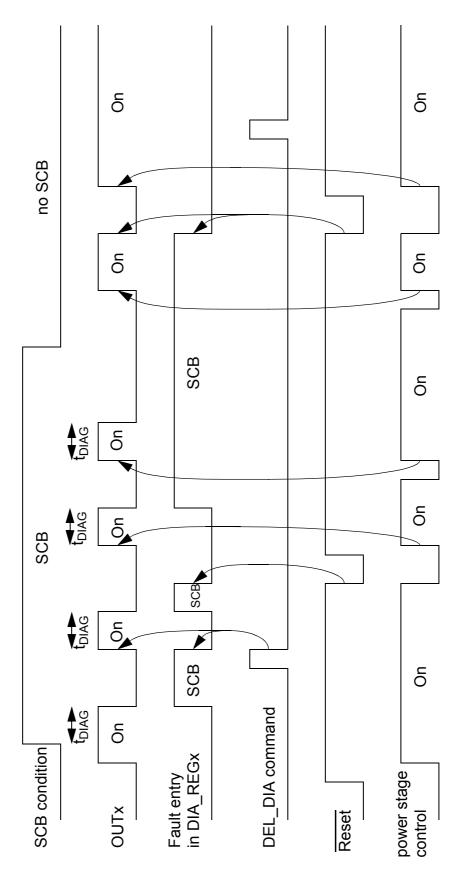

In the case a power stage is shut off because of SCB, the output is activated again by the DEL\_DIA instruction and the filtering-time is enabled. Therefore in case of SCB the output is activated and shut off after the shutoff delay.

For a power stage in the current limitation mode, the current limitation mode is left, if a DEL\_DIA instruction has been received. If there is still the condition for SCB the current limitation mode is entered again.

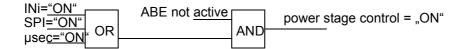

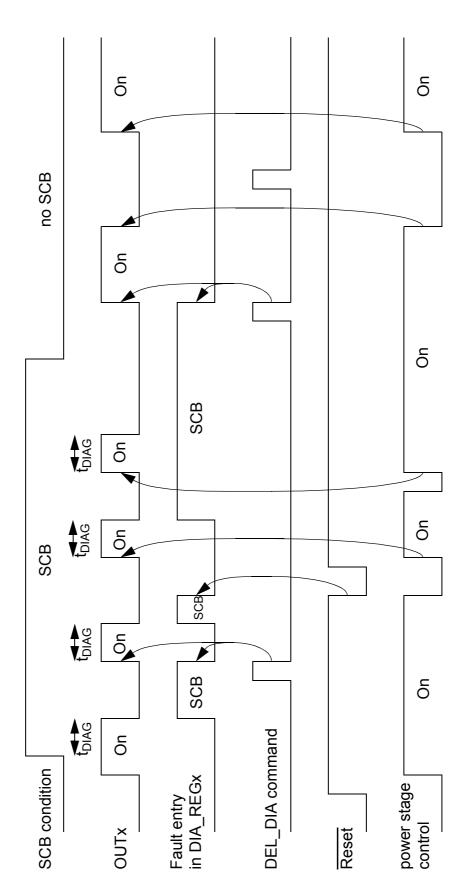

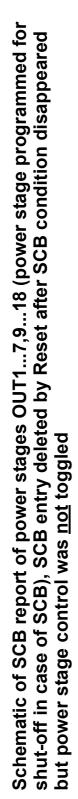

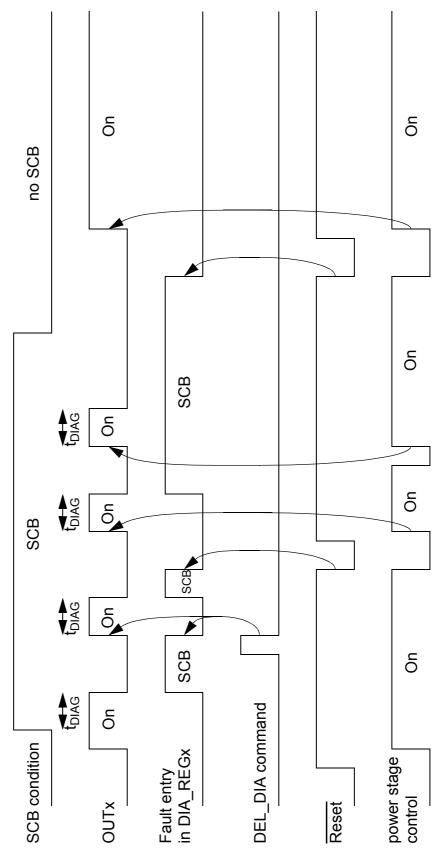

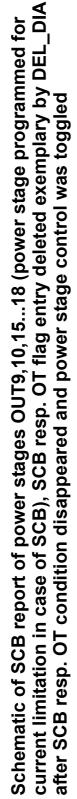

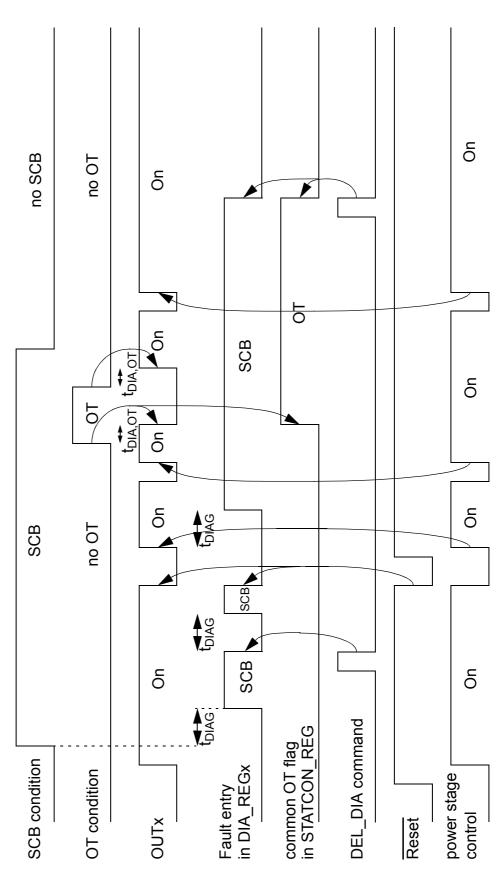

On the following pages the conditions for set and reset of the SCB report in DIA\_REGx is shown in several schematics. The signal "power stage control" is generated as follows:

V7, 2007-06-11

V7, 2007-06-11

V7, 2007-06-11

## Reading Input1 (SPI Instruction: RD\_INP1)

| Registe | er INP_REG1 |   |           |                                                   |     |     |     |  |  |

|---------|-------------|---|-----------|---------------------------------------------------|-----|-----|-----|--|--|

| 7       | 6           | 5 | 4         | 3                                                 | 2   | 1   | 0   |  |  |

| IN8     | Test        | 0 | IN5       | IN4                                               | IN3 | IN2 | IN1 |  |  |

| Bit     | Name        |   | Descrip   | tion                                              |     |     |     |  |  |

| 04      | IN(15)      |   | Status of | Status of the input pins IN1 IN5                  |     |     |     |  |  |

| 5       |             |   | No funct  | No function: LOW on reading                       |     |     |     |  |  |

| 6       | Test        |   | µsec-tes  | µsec-test-bit, the bit D8 of the µsec-bus is read |     |     |     |  |  |

| 7       | IN8         |   | Low leve  | status of the<br>el at pin IN8:<br>el at pin IN8: |     | 3:  |     |  |  |

#### Reading Input2 (SPI Instruction: RD\_INP2):

| Registe | er INP_REG2 |      |                                  |             |         |      |     |

|---------|-------------|------|----------------------------------|-------------|---------|------|-----|

| 7       | 6           | 5    | 4                                | 3           | 2       | 1    | 0   |

| 0       | IN15        | IN14 | IN13                             | IN12        | IN11    | IN10 | IN9 |

| D:4     | News        |      | Decerin                          | 41 o        |         |      |     |

| Bit     | Name        |      | Descrip                          | tion        |         |      |     |

| 06      | IN9IN15     |      | Status of the input pins IN9IN15 |             |         |      |     |

| 7       |             |      | No funct                         | ion: LOW on | reading |      |     |

The input pins IN1..IN5 and IN8...IN15 can be used as input port expander by reading the status of the input pins using the SPI-commands RD\_INP1/2. If the µsec-bus-interface is enabled (BMUX=0) the pull-up current sources at the input IN1..5 and IN9..15 are disabled. If BMUX=1 the pullup current sources at these pins are enabled. The pull-up/pull-down current sources of the other input pins are not effected by the bit BMUX.

On executing the read instruction on RD\_INP1/2, the present status (not latched) of the input pins INx is read back (exception: bit IN8 represents the **inverted** status of input pin IN8).

# Reading the State resp. the Configuration: (SPI Instructions: WR\_STATCON, RD\_STATCON)

| Register | : STATCO | N_REG   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |                                                                          |                                     |          |

|----------|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------|----------|

| 7        | 6        | 5       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                                 | 2                                                                        | 1                                   | 0        |

| CONFIG2  | CONFIG1  | CONFIG0 | STATUS4                                                                                                                                                                                                                                                                                                                                                                                                                                                               | STATUS3                                           | STATUS2                                                                  | STATUS1                             | STATUS0  |

| Bit      | Name     |         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                   |                                                                          |                                     |          |

| 0        | STATUS0  |         | Bit = 1: No overvoltage at VDDBit = 0: Overvoltage at VDD resp. state of overvoltage still<br>stored (reset by CONFIG0 = 0)Access by Controller:Read onlyOvervoltage information (bit STATUS0 = 0) will not be reset by an<br>external reset signal (pin RST=low). Overvoltage will be detected<br>and stored (CONFIG0 = 1) during RST=low. The information will be<br>deleted when an internal (undervoltage) reset occurs or when<br>CONFIG0 is set to 0.           |                                                   |                                                                          |                                     |          |

| 1        | STATUS1  |         | Bit = 1: No undervoltage at VDD<br>Bit = 0: Undervoltage at VDD<br>Access by Controller: Read only                                                                                                                                                                                                                                                                                                                                                                    |                                                   |                                                                          |                                     |          |

| 2        | STATUS2  | 2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ne voltage lev<br>y Controller                    | vel at ABE<br>: Read only                                                | y                                   |          |

| 3        | STATUS   | 3       | nc<br>Bit = 0: Fo<br>det<br>re                                                                                                                                                                                                                                                                                                                                                                                                                                        | present no e<br>ostic registers<br>or at least at | error is entere<br>DIA_REG1<br>one power s<br>ntered in the<br>Read only | 5.<br>tage an erroi<br>correspondii | has been |

| 4        | STATUS4  |         | Common overtemperature flag<br>Bit = 1: No overtemperature detected since the last reset<br>of diagnostic information (by del_dia instruction,<br>RST = Low or undervoltage at VDD (see 3.2. ))<br>Bit = 0: Overtemperature for at least one power stage has<br>been detected since the last reset of the<br>diagnostic information (by del_dia instruction,<br>RST = Low or undervoltage at VDD (see 3.2. ))<br>State of Reset: 1<br>Access by Controller: Read only |                                                   |                                                                          |                                     |          |

| 5        | CONFIG   | )       | Bit = 0: La<br>State of R                                                                                                                                                                                                                                                                                                                                                                                                                                             | tch function f                                    | for overvoltag<br>for overvoltag<br>: Read/Wri                           | ge at VDD is                        |          |

| 6 | CONFIG1 | Bit = 1: Lower threshold of VDD-monitoring is lifted<br>if bit CONFIG2 = 0 (test of switch-off path)<br>Bit = 0: Upper threshold of VDD-monitoring is reduced<br>if bit CONFIG2 = 0 (test of switch-off path)<br>State of Reset: 1<br>Access by Controller: Read/Write |

|---|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 | CONFIG2 | Bit = 1: Test of VDD threshold is switched off<br>Bit = 0: Test of VDD threshold is switched on<br>State of Reset: 1<br>Access by Controller: Read/Write                                                                                                               |

#### 1.7 µsec - Bus Interface

The µsec-bus-interface is one of three possibilities to control the power stages. OUT1...OUT7 and OUT9...OUT16 are influenced by the reset input RST. If RST is set to Low, these power stages are switched off. After reset they are controlled by the SPI (default initialization of TLE6244X). Power stage 8 however is not influenced by the reset input if it's controlled by IN8 and  $U_{VDD} \ge 3,5V$ . Alternatively these outputs can be controlled either by the pins IN1...IN16 or by the µsec-bus interface. Exception: OUT8 can be controlled by IN8 or by the SPI-interface only. The bit 'Bus-Multiplex' (BMUX) in the SPI register CONFIG prescribes parallel access (IN1...IN7, IN9...IN16) or µsec-bus control (see figure below). Exception: If BMUX is set to '0' only the power-stages OUT1...OUT7 and OUT9...OUT16 are controlled by the µsec-bus.

#### Main features:

- 16 data bits for each data-frame (at the pin FDA)

- 16 clock-pulses for each data-frame (at the pin FCL)

- clock frequency TLE6244: 0...16 MHz

- one sync -input (pin SSY) to latch the input data stream

- input level interface same as for IN6, IN7, IN16

- no error correction

When the bit BMUX in CONFIG is set to Low, the power stages 1...7 and 9...16 are controlled by the  $\mu$ sec-bus-interface on condition that registers MUX\_REG1/2 are configured for serial access. The received  $\mu$ sec-bus bit stream (D0... D15) is latched into a 16-bit register by the rising edge at SSY. Power stages 1...7 and 9...16 are switched according to bits D0...D7 and D9...D15:

| µsec-bus | control of power stage | µsec-bus | control of power stage |

|----------|------------------------|----------|------------------------|

| D0       | OUT14                  | D8       | µsec-bus Test<br>Bit   |

| D1       | OUT1                   | D9       | OUT11                  |

| D2       | OUT2                   | D10      | OUT10                  |

| D3       | OUT3                   | D11      | OUT9                   |

| D4       | OUT4                   | D12      | OUT12                  |

| D5       | OUT5                   | D13      | OUT13                  |

| D6       | OUT6                   | D14      | OUT16                  |

| D7       | OUT7                   | D15      | OUT15                  |

| Bit Dx = 0:     | Power stage OUTx is switched on  |

|-----------------|----------------------------------|

| Bit Dx = 1:     | Power stage OUTx is switched off |

| State of reset: | FFFFH                            |

Because the power stage 8 is not controlled by the µsec-bus-interface, the corresponding bit D8 can be used as test bit, that can be read back by the SPI-interface (see register RD\_INP1). If the µsec-bus-interface is used to control the power stages, the input pins IN1..IN5 and IN8...IN15 can be used as input port expander by reading the status of the input pins by the SPI-commands RD\_INP1/2.

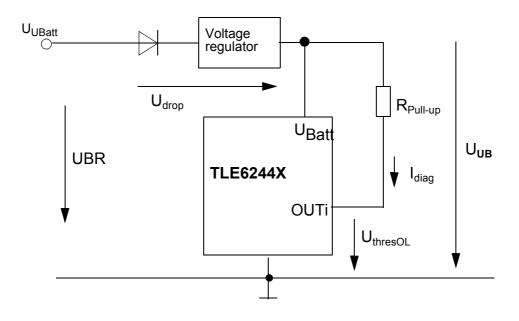

#### 1.8 Unused Power Stages

To avoid an "open load" fault indication an unused power switch has to be connected to an external pull up resistor connected to  $U_{UB}$  or has to be switched on by the input pin or via SPI or the µsec-bus-interface.

R<sub>Pull-up,max</sub> = (UBR<sub>min</sub> - U<sub>drop,max</sub> - U<sub>thresOL,max</sub>) / I<sub>diag,max</sub>

UBR<sub>min</sub> is the required minimum battery voltage for diagnostic function of the ECU. The drop voltage is composed of the drop voltage of the regulator and the drop voltage of the reverse protection circuit of the regulator resp. the forward voltage of a reverse protection diode.

#### Attention:

This equation also applies to power switches that are used as signal drivers (pull up resistor inside ECU or outside ECU): the permissible pull up resistance without a wrong diagnostic information is calculated by the same equation. On dimensioning the pull up resistance in combination with the diagnostic current, in applications as signal drivers attention must be paid especially to the required high level (also for low battery voltage).

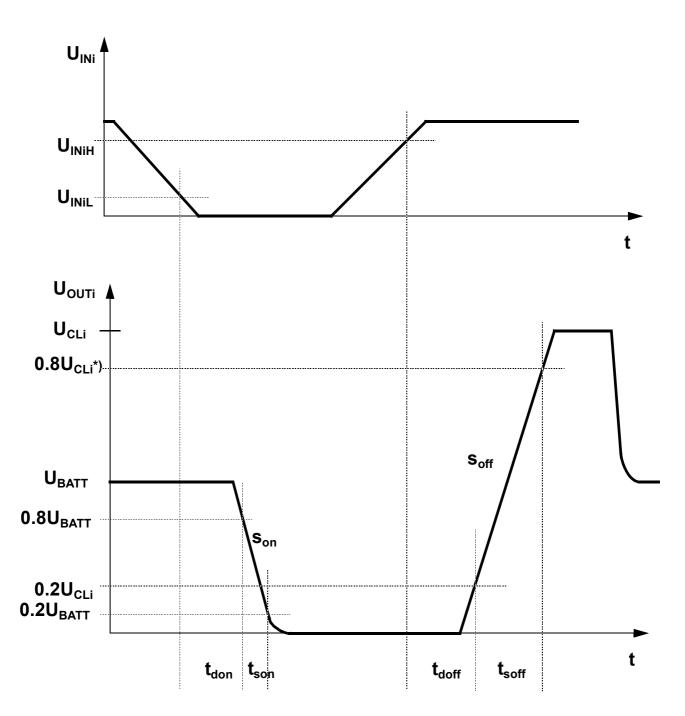

### **1.9 Timing Diagram of the Power Outputs**

1.9.1 Power Stages

If the output is controlled via SPI the timing starts with the positive slope at SS If the output is controlled by the µsec-bus, the timing starts with the pos. slope of SSY \*) With ohmic load, UCLi = UBatt

#### 1.10 VDD-Monitoring

#### **Overview:**

The VDD-monitoring generates a "low" signal at the bidirectional pin  $\overline{ABE}$  if the 5V supply voltage at pin VDD is out of the permissible range of 4.5V...5.5V. On  $\overline{ABE}$  = low the power stages of TLE6244X are switched off. Exception: OUT8 is not switched off in case of parallel control via IN8 by the VDD monitoring undervoltage threshold, but by a threshold of 3.5V at VDD. On shorting pin  $\overline{ABE}$  to V<sub>DD</sub> or UBATT ( $\leq$  36V), the power stages will be switched off in case of undervoltage at pin VDD in spite of  $\overline{ABE}$  = high.

The behavior of the ABE level on the return of VDD out of the undervoltage range into the correct range is not configurable. At the transition from undervoltage to normal voltage the signal at pin ABE goes high after a filtering time is expired. The behavior of the ABE level on the return of VDD out of the overvoltage range into the correct range is configurable in

STATCON\_REG, Bit5. At the transition from overvoltage to normal voltage the signal at pin ABE goes high either after a filtering time (OV not latched) or after a SPI writing instruction (OV latched, state after reset).

On undervoltage condition the signal at pin ABE goes high after a filtering time is expired. On overvoltage condition pin ABE goes high either after a filtering time or after a SPI writing instruction. Before this SPI instruction is sent to TLE6244X appropriate tests can be carried out by the controller.

If the voltage at pin VDD is below the lower limit or is resp. was above the upper limit, this can be read out by the SPI instruction RD\_STATCON.

VDD-monitoring has **no** influence on SCON\_REGx, MUX\_REGx, DIA\_REGx, CONFIG and INP\_REGx.

If output stages are switched off by the internal over-/undervoltage detection or by externally applying a low signal at the ABE pin, no failure storage (DIAREG1...5) may occur.

#### **Description in Detail:**

Description of the Register: STATCON\_REG

- Bit 7 1: Normal operation 0: Test of VDD threshold Access by controller: read/write State of reset: 1

- Bit 6 1: Testing the lower threshold (if bit 7 = 0) 0: Testing the upper threshold (if bit 7 = 0) Access by controller: read/write State of reset: 1

- Bit 5 1: <u>ABE</u> latched after overvoltage 0: <u>ABE</u> deactivated immediately after the disappearance of the overvoltage Access by controller: read/write State of reset: 1

- Bit 2 Reading out the level at pin ABE Access by controller: read only

- Bit 1 1: no undervoltage at pin VDD 0: undervoltage at pin VDD Access by controller: read only

Bit 0

1: no overvoltage at pin VDD

0: overvoltage at pin VDD resp. state of overvoltage still stored

Access by controller: read only

#### Testing the VDD-Monitoring:

#### Upper threshold:

By writing 000xxxxx<sub>b</sub> in the register STATCON\_REG the overvoltage threshold is reduced by 0.8V. In STATCON\_REG Bit 0 has to be LOW then.

After writing 110xxxxx<sub>b</sub> in the register STATCON\_REG Bit 0 in STATCON\_REG must be HIGH again.

Lower threshold:

By writing  $010xxxxb_b$  in the register STATCON\_REG the overvoltage threshold is increased by 0.8V. In STATCON\_REG Bit 1 has to be LOW then.

After writing 110xxxxx<sub>b</sub> in the register STATCON\_REG Bit 1 in STATCON\_REG must be HIGH again.

Example of configuration:

Requirement: After overvoltage  $\overline{ABE}$  is to be LOW; After overvoltage a self-test is carried out by the ECU, afterwards  $\overline{ABE}$  is deactivated.

Register STATCON\_REG is set to 111xxxxxb during driving cycle.

When  $\overline{\text{ABE}}$  becomes active, overvoltage can be detected by reading out STATCON\_REG. After the ECU's self-test a reset condition is achieved by writing  $110xxxxx_b$  into the register STATCON\_REG. This reset is only possible after disappearance of the overvoltage condition because the set input is dominant. The reset signal is withdrawn by writing  $111xxxxx_b$ .

#### 1.11 Notes for the Application in Commercial Vehicles

## For electric systems with 24V battery voltage, that can even increase to $\geq$ 37V in case of load dump, some peculiarities have to be observed!

The static voltage at pin UBatt without destruction is limited to 37V, therefore this pin must either be connected to the 5V supply voltage VDD or else the voltage at pin UBatt has to be limited by adequate external circuitry. By connecting pin UBatt to VDD the values of  $R_{ds, on}$  of the power switches will increase up to 20%.

The power stages 7...18 are equipped with a 40V active clamping. Therefore this power stages must only drive loads with an accordingly high resistance that can be switched on in case of overvoltage (e.g. a maximum load dump voltage of 60V and a load resistor of  $1k\Omega$  result in a power dissipation of 0.8W for each power stage. For all of the 12 power stages together there is a power dissipation of 9.6W for the typical duration of a load dump of 500ms.).

# The restrictions listed above are no longer relevant in case of a "overvoltage-protected battery voltage"within the 24V electric system that limits the voltage to e.g. a maximum of 37V.

The thresholds of the currents, on which the power stages are switched off in case of overload, are increased by approximately 25% if there is a voltage at pin UBatt higher than19V (reason: jump start requirements in 12V electric systems). Exception: OUT9 and OUT10 and OUT15... OUT18. See characteristics in chapters 3.5.3, 3.6.3, 3.7.3 and 3.8.3.

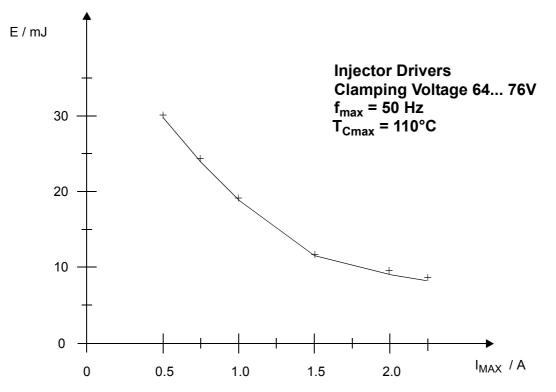

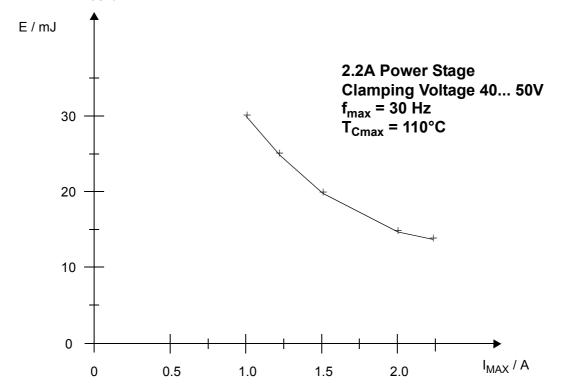

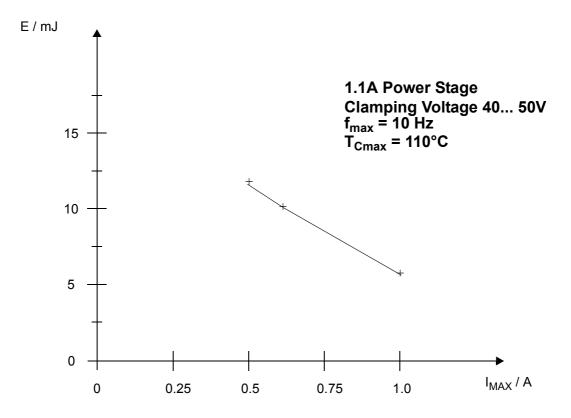

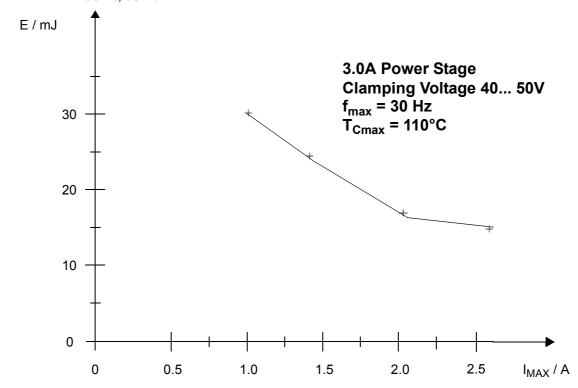

The restrictions concerning overload of power stages (see 3.5.2, 3.6.2, 3.7.2 and 3.8.2) and permissible clamping energy (see 3.5.8, 3.6.8, 3.7.8 and 3.8.8) are relevant further on.

#### 1.11.1 Notes for short circuit limitation

The power stages are short circuit protected for the following conditions:

The max. voltage at the output pins are limited to 36V and the TLE6244 is not operating in the booster mode.

The power stages will be switched on/off with a max. frequency of 1 kHz.

Only a 40 msec burst with the 1 kHz on/off-frequency is allowed, with a minimum burst repetition time of 1 sec. The maximum number of burst repetition cycles is 25. The number of driving cycles under these conditions is limited to 100 in lifetime. The temperature of the slug of the PG-MQFP-64

package must not exceed 130°C.

These limitations are valid for UBatt > 24 V.

For Ubatt  $\leq$  24 V the number of driving cycles under these conditions is extended to 1000 in lifetime.

#### 1.12 Notes for the Diagnostics

- SCB entry in DIA\_REGx see diagrams in chapter 1.6.4.

- In case of overvoltage at pin VDD (VDD > 5,5V) the diagnostic information can be wrong. In that case, the diagnostic information has to be cleared with the DEL\_DIA instruction.

- The filtering time restarts when the output voltage passes the diagnostic threshold for short to ground (SCG).

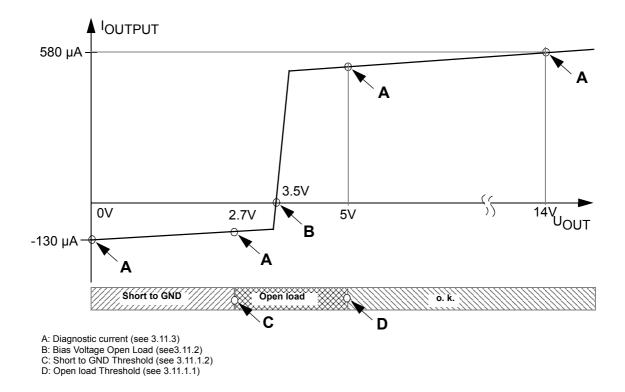

- Diagram of the typical diagnostic current:

## State Diagram of the Power Stages Diagnostics

At DEL\_DIA: C -> B D -> B A no action

Exemplary for a power stage controlled by input pin INx. Diagram is accordingly valid for serial con-

#### **1.13 Parallel Connection of Power Stages**

The power stages (PS) which are connected in parallel have to be switched on and off simultaneously. The corresponding SPI-Bits SCONx have to be in the same register (see page 15), when the PS are serial controlled via SPI.

In case of overload the ground current and the power dissipation are increasing. The application has to take into account that all maximum ratings are observed (e.g. operating temperature  $T_J$  and total ground current  $I_{GND}$ , see page 36, 37).

Max. number of parallel connections: 3

#### The following statements apply to PS within the same TLE6244X

The max. short circuit shutdown threshold of the parallel connected PS is the summation of the corresponding max. values of the PS ( $I_{SC,OUTx} + I_{SC,OUTy} + ...$ ).

|                                                                                                                                              | Max. Nominal Current                                                                | Max. Clamping Energy                                                | On Resistance                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|

| 2 symmetrical PS<br>(see note 1)                                                                                                             | 0.9 x (I <sub>max,OUTx</sub> + I <sub>max,OUTy</sub> )                              | 0.75 x (E <sub>CI,OUTx</sub> + E <sub>CI,OUTy</sub> )               | 0.5 x R <sub>on,OUTx,y</sub>                                       |

| 2 PS of the same type<br>(see note 2)                                                                                                        | 0.85 x (I <sub>max,OUTx</sub> + I <sub>max,OUTy</sub> )                             | 0.75 x (E <sub>CI,OUTx</sub> + E <sub>CI,OUTy</sub> )               | 0.5 x R <sub>on,OUTx,y</sub>                                       |

| 3 PS of the same type<br>(see note 2)                                                                                                        | 0,8 x<br>(Imax,OUTx <sup>+ I</sup> max,OUTy <sup>+</sup><br>I <sub>max,OUTz</sub> ) | 0,58 x<br>(ECI,OUTx <sup>+</sup> ECI,OUTy <sup>+</sup><br>ECI,OUTz) | 0.34 x<br>Ron,OUTx,y,z                                             |

| 2 PS with the same nominal<br>current, but different clamp-<br>ing voltage (application with-<br>out<br>free-wheeling-diode)<br>(see note 3) | 0.7 x (I <sub>max,OUTx</sub> + I <sub>max,OUTy</sub> )                              | Clamping energy<br>of the PS with the lower<br>clamping voltage     | Ron,OUTx X Ron,OUTy<br>Ron,OUTx + Ron,OUTy                         |

| 2 PS with the same nominal<br>current, but different clamp-<br>ing voltage (application with<br>free-wheeling-diode)<br>(see note 3)         | 0.7 x (I <sub>max,OUTx</sub> + I <sub>max,OUTy</sub> )                              | no clamping required                                                | Ron,OUTx <sup>x</sup> Ron,OUTy<br>Ron,Ax <sup>+ R</sup> on,OUTy    |

| 2 PS with the same clamp-<br>ing voltage, but different<br>nominal<br>current (see note 4)                                                   | Max<br>Max<br>Imax,OUTy<br>0.75 x (Imax,OUTx +<br>Imax,OUTy)                        | Min ECI,OUTX<br>ECI,OUTy                                            | Ron,OUTx X Ron,OUTy<br>Ron,OUTx + Ron,OUTy                         |