### **INTEGRATED CIRCUITS**

# DATA SHEET

For a complete data sheet, please also download:

- The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC

- The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC

# HEF4521B MSI

24-stage frequency divider and oscillator

Product specification

File under Integrated Circuits, IC04

January 1995

## 24-stage frequency divider and oscillator

HEF4521B MSI

#### **DESCRIPTION**

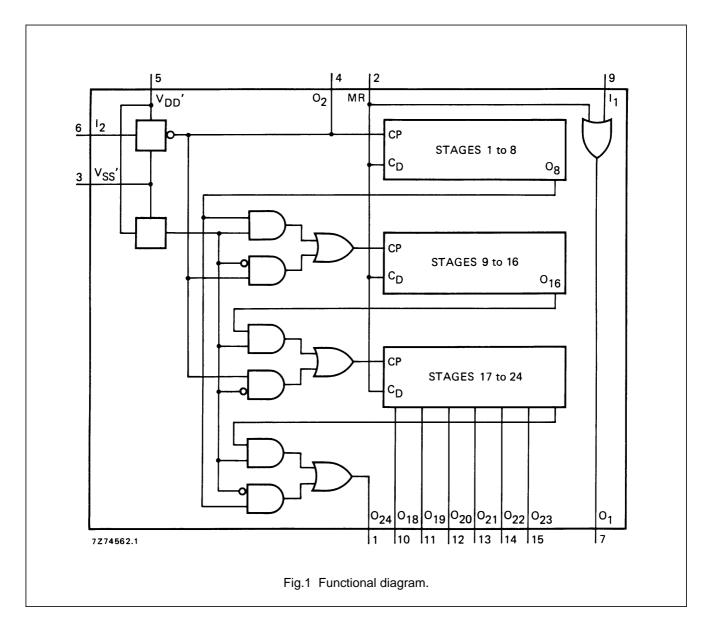

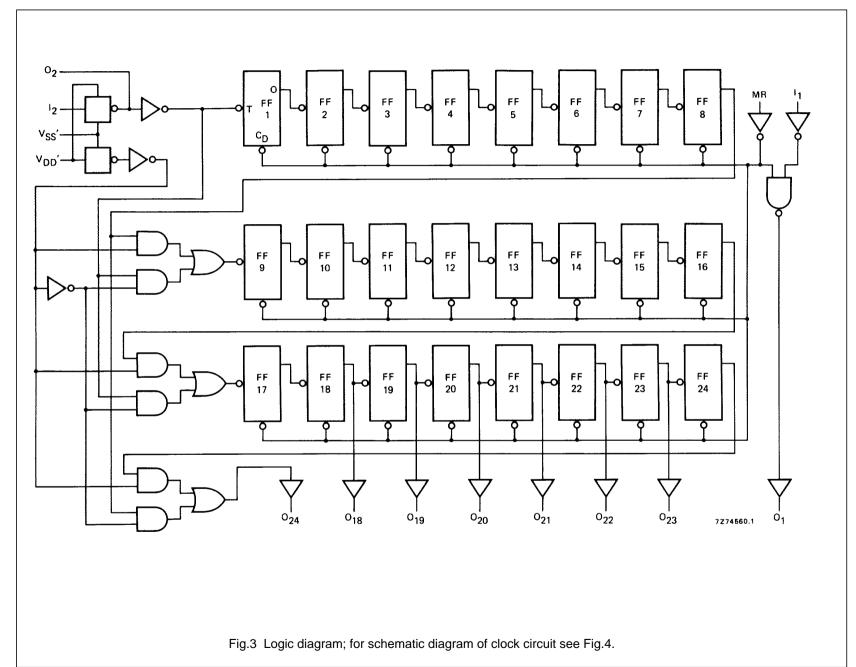

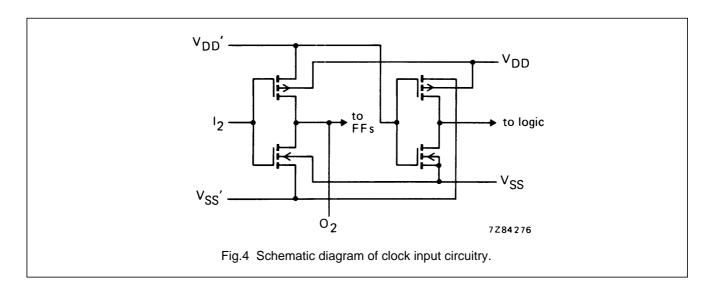

The HEF4521B consists of a chain of 24 toggle flip-flops with an overriding asynchronous master reset input (MR), and an input circuit that allows three modes of operation. The single inverting stage ( $I_2/O_2$ ) will function as a crystal oscillator, or in combination with  $I_1$  as an RC oscillator, or as an input buffer for an external oscillator. Low-power

operation as a crystal oscillator is enabled by connecting external resistors to pins 3 ( $V_{SS}$ ') and 5 ( $V_{DD}$ '). Each flip-flop divides the frequency of the previous flip-flop by two, consequently the HEF4521B will count up to  $2^{24}$  = 16777216. The counting advances on the HIGH to LOW transition of the clock ( $I_2$ ). The outputs of the last seven stages are available for additional flexibility.

#### FAMILY DATA, I<sub>DD</sub> LIMITS category MSI

See Family Specifications

## 24-stage frequency divider and oscillator

HEF4521B MSI

#### **COUNT CAPACITY**

| ОИТРИТ          | COUNT CAPACITY               |

|-----------------|------------------------------|

| O <sub>18</sub> | 2 <sup>18</sup> = 262 144    |

| O <sub>19</sub> | 2 <sup>19</sup> = 524 288    |

| O <sub>20</sub> | 2 <sup>20</sup> = 1 048 576  |

| O <sub>21</sub> | 2 <sup>21</sup> = 2 097 152  |

| O <sub>22</sub> | 2 <sup>22</sup> = 4 194 304  |

| O <sub>23</sub> | 2 <sup>23</sup> = 8 388 608  |

| O <sub>24</sub> | 2 <sup>24</sup> = 16 777 216 |

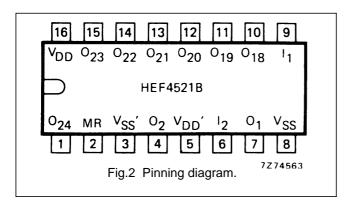

HEF4521BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4521BD(F): 16-lead DIL; ceramic (cerdip) (SOT74) HEF4521BT(D): 16-lead SO; plastic (SOT109-1)

(): Package Designator North America

#### **FUNCTIONAL TEST SEQUENCE**

| INPL | JTS            |                | CONTROL<br>TERMINALS | <b>,</b>          | OUTPUTS                            | REMARKS                                                                                                                                                           |

|------|----------------|----------------|----------------------|-------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MR   | l <sub>2</sub> | O <sub>2</sub> | V <sub>SS</sub> '    | V <sub>DD</sub> ' | O <sub>18</sub> to O <sub>24</sub> |                                                                                                                                                                   |

| Н    | L              | L              | V <sub>DD</sub>      | V <sub>SS</sub>   | L                                  | counter is in three 8-stage sections in parallel mode; I <sub>2</sub> and O <sub>2</sub> are interconnected (O <sub>2</sub> is now input); counter is reset by MR |

| L    | Л              | Л              | V <sub>DD</sub>      | V <sub>SS</sub>   | Н                                  | 255 pulses are clocked into I <sub>2</sub> , O <sub>2</sub> (the counter advances on the LOW to HIGH transition)                                                  |

| L    | L              | L              | V <sub>SS</sub>      | V <sub>SS</sub>   | Н                                  | V <sub>SS</sub> ' is connected to V <sub>SS</sub>                                                                                                                 |

| L    | Н              | L              | V <sub>SS</sub>      | V <sub>SS</sub>   | Н                                  | the input I <sub>2</sub> is made HIGH                                                                                                                             |

| L    | Н              | L              | V <sub>SS</sub>      | V <sub>DD</sub>   | Н                                  | V <sub>DD</sub> ' is connected to V <sub>DD</sub> ; O <sub>2</sub> is now made floating and becomes an output; the device is now in the 2 <sup>24</sup> mode      |

| L    | ~              |                | V <sub>SS</sub>      | V <sub>DD</sub>   | L                                  | counter ripples from an all HIGH state to an all LOW state                                                                                                        |

A test function has been included for the reduction of the test time required to exercise all 24 counter stages. This test function divides the counter into three 8-stage sections by connecting  $V_{SS}$  to  $V_{DD}$  and  $V_{DD}$  to  $V_{SS}$ . Via  $I_2$  (connected to  $O_2$ ) 255 counts are loaded into each of the 8-stage sections in parallel. All flip-flops are now at a HIGH state.

The counter is now returned to the normal 24-stage in series configuration by connecting  $V_{SS}$ ' to  $V_{SS}$  and  $V_{DD}$ ' to  $V_{DD}$ . One more pulse is entered into input  $I_2$ , which will cause the counter to ripple from an all HIGH state to an all LOW state.

Philips Semiconductors

# 24-stage frequency divider and oscillator

HEF4521B MSI

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                           | V <sub>DD</sub> | SYMBOL           | MIN. | TYP. | MAX. |    | TYPICAL<br>EXTRAPOLATION<br>FORMULA  |  |

|---------------------------|-----------------|------------------|------|------|------|----|--------------------------------------|--|

| Propagation delays        |                 |                  |      |      |      |    |                                      |  |

| $I_2 \rightarrow O_{18}$  | 5               |                  |      | 950  | 1900 | ns | 923 ns + (0,55 ns/pF) C <sub>L</sub> |  |

| HIGH to LOW               | 10              | t <sub>PHL</sub> |      | 350  | 700  | ns | 339 ns + (0,23 ns/pF) C <sub>L</sub> |  |

|                           | 15              |                  |      | 220  | 440  | ns | 212 ns + (0,16 ns/pF) C <sub>L</sub> |  |

|                           | 5               |                  |      | 950  | 1900 | ns | 923 ns + (0,55 ns/pF) C <sub>L</sub> |  |

| LOW to HIGH               | 10              | t <sub>PLH</sub> |      | 350  | 700  | ns | 339 ns + (0,23 ns/pF) C <sub>L</sub> |  |

|                           | 15              |                  |      | 220  | 440  | ns | 212 ns + (0,16 ns/pF) C <sub>L</sub> |  |

| $O_n \rightarrow O_n + 1$ | 5               |                  |      | 40   | 80   | ns | 13 ns + (0,55 ns/pF) C <sub>L</sub>  |  |

| HIGH to LOW               | 10              | t <sub>PHL</sub> |      | 15   | 30   | ns | 4 ns + (0,23 ns/pF) C <sub>L</sub>   |  |

|                           | 15              |                  |      | 10   | 20   | ns | 2 ns + (0,16 ns/pF) C <sub>L</sub>   |  |

|                           | 5               |                  |      | 40   | 80   | ns | 13 ns + (0,55 ns/pF) C <sub>L</sub>  |  |

| LOW to HIGH               | 10              | t <sub>PLH</sub> |      | 15   | 30   | ns | 4 ns + (0,23 ns/pF) C <sub>L</sub>   |  |

|                           | 15              |                  |      | 10   | 20   | ns | 2 ns + (0,16 ns/pF) C <sub>L</sub>   |  |

| $MR \to O_n$              | 5               |                  |      | 120  | 240  | ns | 93 ns + (0,55 ns/pF) C <sub>L</sub>  |  |

| HIGH to LOW               | 10              | t <sub>PHL</sub> |      | 55   | 110  | ns | 44 ns + (0,23 ns/pF) C <sub>L</sub>  |  |

|                           | 15              |                  |      | 40   | 80   | ns | 32 ns + (0,16 ns/pF) C <sub>L</sub>  |  |

| $I_1 \rightarrow O_1$     | 5               |                  |      | 90   | 180  | ns | 63 ns + (0,55 ns/pF) C <sub>L</sub>  |  |

| HIGH to LOW               | 10              | t <sub>PHL</sub> |      | 35   | 70   | ns | 24 ns + (0,23 ns/pF) C <sub>L</sub>  |  |

|                           | 15              |                  |      | 25   | 50   | ns | 17 ns + (0,16 ns/pF) C <sub>L</sub>  |  |

|                           | 5               |                  |      | 60   | 120  | ns | 33 ns + (0,55 ns/pF) C <sub>L</sub>  |  |

| LOW to HIGH               | 10              | t <sub>PLH</sub> |      | 30   | 60   | ns | 19 ns + (0,23 ns/pF) C <sub>L</sub>  |  |

|                           | 15              |                  |      | 20   | 40   | ns | 12 ns + (0,16 ns/pF) C <sub>L</sub>  |  |

# 24-stage frequency divider and oscillator

HEF4521B MSI

|                         | V <sub>DD</sub><br>V | SYMBOL           | MIN. | TYP. | MAX. |    | TYPICAL<br>EXTRAPOLATION<br>FORMULA |  |  |

|-------------------------|----------------------|------------------|------|------|------|----|-------------------------------------|--|--|

| Output transition times | 5                    |                  |      | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |  |  |

| HIGH to LOW             | 10                   | t <sub>THL</sub> |      | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |  |  |

|                         | 15                   |                  |      | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |  |  |

|                         | 5                    |                  |      | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |  |  |

| LOW to HIGH             | 10                   | t <sub>TLH</sub> |      | 30   | 60   | ns | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |  |  |

|                         | 15                   |                  |      | 20   | 40   | ns | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |  |  |

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                              | V <sub>DD</sub> | SYMBOL            | MIN. | TYP. | MAX. |                             |

|------------------------------|-----------------|-------------------|------|------|------|-----------------------------|

| Minimum I <sub>2</sub> pulse | 5               |                   | 80   | 40   | ns   |                             |

| width; HIGH                  | 10              | t <sub>WI2H</sub> | 40   | 20   | ns   |                             |

|                              | 15              |                   | 30   | 15   | ns   |                             |

| Minimum MR                   | 5               |                   | 70   | 35   | ns   |                             |

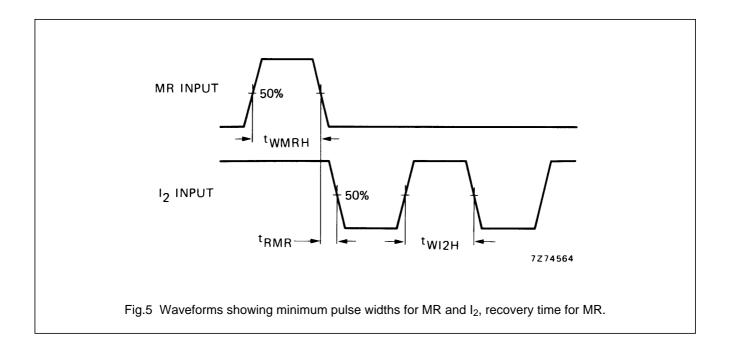

| pulse width; HIGH            | 10              | t <sub>WMRH</sub> | 40   | 20   | ns   | see also waveforms<br>Fig.5 |

|                              | 15              |                   | 30   | 15   | ns   | i ig.o                      |

| Recovery time                | 5               |                   | 20   | -10  | ns   |                             |

| for MR                       | 10              | t <sub>RMR</sub>  | 15   | -5   | ns   |                             |

|                              | 15              |                   | 15   | 0    | ns   |                             |

| Maximum clock                | 5               |                   | 6    | 12   | MHz  |                             |

| pulse frequency              | 10              | f <sub>max</sub>  | 12   | 25   | MHz  |                             |

|                              | 15              |                   | 17   | 35   | MHz  |                             |

|                 | V <sub>DD</sub> | TYPICAL FORMULA FOR P (μW)                    |                                         |

|-----------------|-----------------|-----------------------------------------------|-----------------------------------------|

| Dynamic power   | 5               | 1 200 $f_i + \sum (f_0 C_L) \times V_{DD}^2$  | where                                   |

| dissipation per | 10              | 5 100 $f_i + \sum (f_0 C_L) \times V_{DD}^2$  | f <sub>i</sub> = input freq. (MHz)      |

| package (P)     | 15              | 13 050 $f_i + \sum (f_o C_L) \times V_{DD}^2$ | f <sub>o</sub> = output freq. (MHz)     |

|                 |                 |                                               | C <sub>L</sub> = load capacitance (pF)  |

|                 |                 |                                               | $\sum (f_0C_L) = \text{sum of outputs}$ |

|                 |                 |                                               | V <sub>DD</sub> = supply voltage (V)    |

# 24-stage frequency divider and oscillator

HEF4521B MSI

# 24-stage frequency divider and oscillator

HEF4521B MSI

#### **APPLICATION INFORMATION**

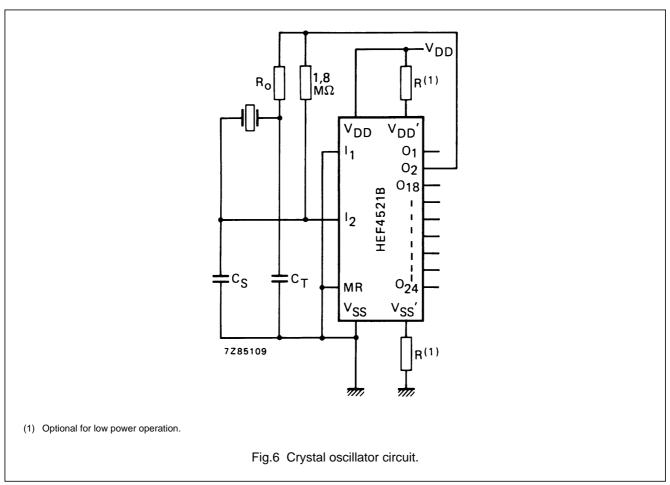

Typical characteristics for crystal oscillator circuit (Fig.6):

|                                       | 500 kHz<br>CIRCUIT | 50 kHz<br>CIRCUIT | UNIT |

|---------------------------------------|--------------------|-------------------|------|

| Crystal characteristics               |                    |                   |      |

| resonance frequency                   | 500                | 50                | kHz  |

| crystal cut                           | S                  | N                 | _    |

| equivalent resistance; R <sub>S</sub> | 1                  | 6,2               | kΩ   |

| External resistor/capacitor values    |                    |                   |      |

| R <sub>o</sub>                        | 47                 | 750               | kΩ   |

| C <sub>T</sub>                        | 82                 | 82                | pF   |

| C <sub>S</sub>                        | 20                 | 20                | pF   |

## 24-stage frequency divider and oscillator

## HEF4521B MSI

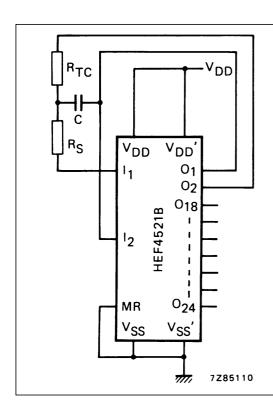

Fig.7 RC oscillator circuit;

$$f \approx \frac{1}{2,3 \times R_{TC} \times C}$$

;  $R_S \ge 2 R_{TC}$ , in which:

f in Hz, R in  $\Omega$ , C in F.

$$R_S + R_{TC} < \frac{V_{IL \ max}}{I_{LI}}$$

(maximum input voltage LOW) (input leakage current)

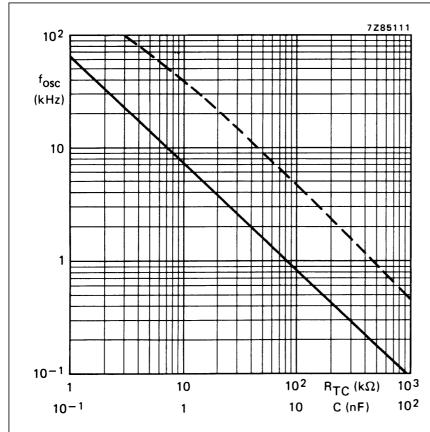

Fig.8 Oscillator frequency as a function of  $R_{TC}$  and C;  $V_{DD} = 10 \text{ V}$ ; test circuit is Fig.7.

# 24-stage frequency divider and oscillator

HEF4521B MSI

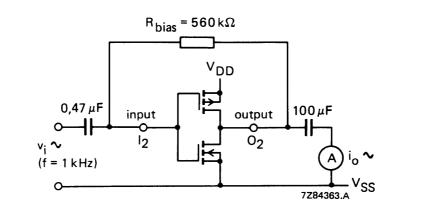

Fig.9 Test set-up for measuring forward transconductance  $g_{fs} = di_0/d_{vi}$  at  $v_0$  is constant (see also graph Fig.10).

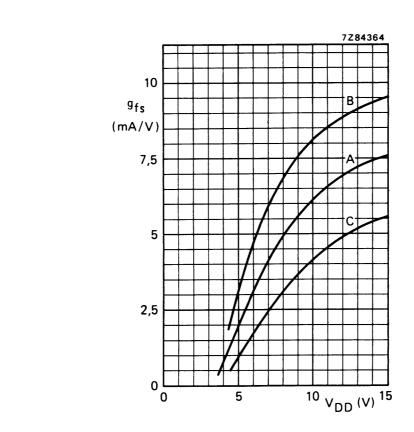

A: average,

B: average + 2 s,

C: average – 2 s, in which: 's' is the observed standard deviation.

Fig.10 Typical forward transconductance  $g_{fs}$  as a function of the supply voltage at  $T_{amb}$  = 25 °C.

# 24-stage frequency divider and oscillator

HEF4521B MSI

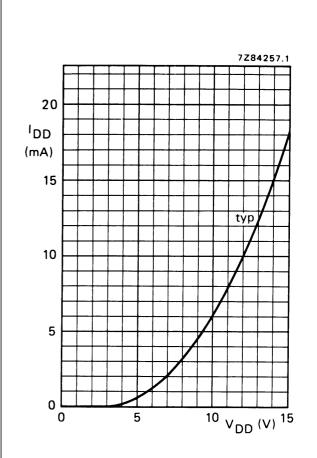

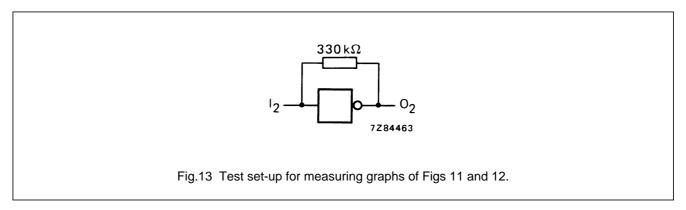

Fig.12 Supply current as a function of supply voltage.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.